# **DPS Power Supply**

A Server System Infrastructure Specification For Distributed Power Systems

Version 2.0

### Disclaimer:

THIS SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE. WITHOUT LIMITATION, THE PROMOTERS (Intel Corporation, NEC Corporation, Dell Computer Corporation, Data General a division of EMC Corporation, Compaq Computer Corporation, Silicon Graphics Inc., and International Business Machines Corporation) DISCLAIM ALL LIABILITY FOR COST OF PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES, LOST PROFITS, LOSS OF USE, LOSS OF DATA OR ANY INCIDENTAL, CONSEQUENTIAL, DIRECT, INDIRECT, OR SPECIAL DAMAGES, WHETHER UNDER CONTRACT, TORT, WARRANTY OR OTHERWISE, ARISING IN ANY WAY OUT OF USE OR RELIANCE UPON THIS SPECIFICATION OR ANY INFORMATION HEREIN.

The Promoters disclaim all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

This specification and the information herein is the confidential and trade secret information of the Promoters. Use, reproduction and disclosure of this specification and the information herein is subject to the terms of the S.S.I. Specification Adopter's Agreement.

Copyright © Intel Corporation, NEC Corporation, Dell Computer Corporation, Data General a division of EMC Corporation, Compaq Computer Corporation, Silicon Graphics Inc., International Business Machines Corporation, 2000.

# Contents

| 1 |    |           | rpose                                                                   |    |

|---|----|-----------|-------------------------------------------------------------------------|----|

| 2 |    | Coi       | nceptual Overview                                                       |    |

|   | 2. |           | Distributed Power Architectural Overview                                |    |

| 3 |    |           | finitions/Terms/Acronyms                                                |    |

| 4 |    |           | neral                                                                   |    |

| 5 |    |           | chanical Overview                                                       |    |

|   | 5. | -         | Connector Locations                                                     |    |

|   | 5. |           | Handle and Retention Mechanism                                          |    |

|   |    | 5.2       |                                                                         |    |

|   | 5. |           | Power Supply Case Keying for Airflow                                    |    |

|   | 5. | -         | Airflow Requirements                                                    |    |

|   |    | 5.4       | I                                                                       |    |

|   | 5. |           | Thermal Requirements                                                    |    |

| _ | 5. |           | Acoustic Requirement                                                    |    |

| 6 |    |           | Input Requirements                                                      |    |

|   | 6. | -         | AC Inlet Connector                                                      |    |

|   | 6. | _         | AC Input Specification                                                  |    |

|   | 6. |           | Efficiency                                                              |    |

|   | 6. |           | AC Multiple Phase Input Capability                                      |    |

|   | 6. | -         | AC Line Dropout                                                         |    |

|   | 6. | -         | AC Brownout Requirement                                                 |    |

|   | 6. |           | AC Line Fuse                                                            |    |

|   | 6. | -         | AC Line Inrush                                                          |    |

|   | 6. | 9<br>10   | Maximum AC Leakage Current to Ground<br>AC Line Transient Specification |    |

|   |    | 10        | AC Line Fast Transient Specification                                    |    |

| 7 |    |           | Output Specification                                                    |    |

| ' | 7. |           | DC Power Connector Requirements                                         |    |

|   | 7. | -         | DC Output Rating                                                        |    |

|   |    | z<br>7.2. |                                                                         |    |

|   | 7. |           | Grounding                                                               |    |

|   | 7. |           | Regulation                                                              |    |

|   | 7. |           | Transient Loading                                                       |    |

|   | 7. | -         | Capacitive Load.                                                        |    |

|   | 7. |           | Ripple and Noise                                                        |    |

|   | 7. |           | 12 VSB                                                                  |    |

|   | 7. | -         | Hot Swap Requirement                                                    |    |

|   |    | -         | 0.1 Output Isolation                                                    |    |

|   |    | 10        | Timing Requirements                                                     |    |

|   |    | 11        | Forced Load Sharing                                                     |    |

|   |    | 7.1       | · · · · · · · · · · · · · · · · · · ·                                   |    |

|   |    | 7.1       | •                                                                       |    |

|   |    | 7.1       |                                                                         |    |

| 8 |    |           | otection Circuits                                                       |    |

|   | 8. |           | Over-voltage Protection                                                 |    |

|   | 8. | 2         | Over-current / Short Circuit Protection                                 |    |

|   | 8. |           | Thermal Protection                                                      | 33 |

| 9 |    | Cor       | ntrol and Indicator Functions                                           | 34 |

|   | 9. | 1         | PSON <sup>#</sup> (Power Supply Enable)                                 | 34 |

# SSI

|           |          | DPS Power Supply Specification, V2.0                  |

|-----------|----------|-------------------------------------------------------|

| 9.2       | 2 PSł    | ill                                                   |

| 9.3       |          | nput Range Setting (ACRange)                          |

| 9.4       |          | 0K <sup>#</sup> Signal                                |

| 9.5       |          | DK (Power Good)                                       |

| 9.6       |          | lictive Failure Signal (PRFL)                         |

| 9.7       |          | er Supply Failure (FAIL)                              |

| 9.8       | B Pov    | er Supply Present Indicator (PRESENT <sup>#</sup> )40 |

| 9.9       |          | Control (FANC)                                        |

| 9.1       |          | Power Input (FANP)                                    |

| 9.1       |          | lert <sup>#</sup>                                     |

| 9.1       |          | er Supply Management (PSM) Interface43                |

| ę         |          | Monitoring Cycle Time                                 |

|           |          | Current Monitoring                                    |

|           | 9.12.3   | Output Voltage Monitoring                             |

| 9         | 9.12.4   | Temperature Monitoring                                |

| 9         | 9.12.5   | Fan Speed Measurement                                 |

| 9         | 9.12.6   | Fan Speed Control                                     |

| ę         | 9.12.7   | Hours in Operation Clock                              |

| ę         | 9.12.8   | Input Voltage Monitoring49                            |

| ę         | 9.12.9   | PSM Interface49                                       |

| ę         | 9.12.10  | PSM Protocols49                                       |

| ę         | 9.12.11  | PSM Write Operations                                  |

| 9         | 9.12.12  | PSM Read Operations51                                 |

| 9         | 9.12.13  | Reset                                                 |

|           | 9.12.14  | Interrupt Status Registers53                          |

| <b>10</b> | Field Re | placement Unit (FRU) Signals54                        |

|           |          | Data54                                                |

| 10        |          | Data Format                                           |

| 10        |          | Indicators                                            |

|           |          | s and Labels                                          |

|           |          | Labeling                                              |

|           |          |                                                       |

| 13        | Agency   | Requirements                                          |

# Figures

| Figure 1: | Distributed Power Scheme Overview | 8  |

|-----------|-----------------------------------|----|

| Figure 2: | Form Factor                       | 10 |

| Figure 3: | External Face                     | 11 |

|           | Side View                         |    |

| Figure 5: | Interior Face                     | 12 |

| Figure 6: | Handle/Retention Mechanism        | 13 |

| Figure 7: | Airflow Keying                    | 14 |

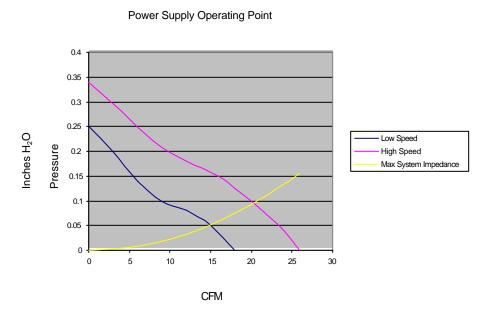

| Figure 8: | Power Supply Airflow P-Q Curve    | 16 |

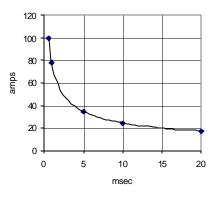

| Figure 9: | Inrush Limit                      | 20 |

| Figure 10 | : DC Output Connector             | 23 |

| Figure 11 | : Turn On/Off Timing              | 29 |

| •         |                                   |    |

# Tables

| Table 1: / | Airflow Requirements                        | 15 |

|------------|---------------------------------------------|----|

| Table 2: 7 | Thermal Requirements                        | 16 |

| Table 3: / | AC Input Voltage                            | 18 |

| Table 4: / | AC Line Sag Transient Performance           | 21 |

|            | AC Line Surge Transient Performance         |    |

|            | Signal Descriptions                         |    |

| Table 7: 0 | Output Connector Pin-out                    | 23 |

| Table 8: I | DC Output Rating                            | 24 |

| Table 9: 4 | 48 VDC Isolation Requirements               | 25 |

| Table 10:  | DC Output Regulation                        | 25 |

| Table 11:  | Transient Response                          | 26 |

| Table 12:  | Capacitive Loading                          | 26 |

| Table 13:  | Ripple and Noise                            | 27 |

| Table 14:  | Turn On/Off Timing                          | 28 |

| Table 15:  | System Load                                 | 30 |

| Table 16:  | Load Share Bus Output Characteristic        | 30 |

| Table 17:  | Standby Load Sharing                        | 31 |

| Table 18:  | Over-voltage Protection Requirements        | 32 |

|            | Over Current Protection                     |    |

| Table 20:  | PSON <sup>#</sup> Signal Characteristic     | 34 |

| Table 21:  | PSKill Signal Characteristics               | 35 |

| Table 22:  | ACRange Signal Characteristic               | 36 |

|            | ACOK <sup>#</sup> Signal Characteristics    |    |

| Table 24:  | PWOK Signal Characteristics                 | 38 |

|            | PRFL Signal Characteristics                 |    |

| Table 26:  | FAIL Signal Characteristics                 | 39 |

|            | PRESENT <sup>#</sup> Signal Characteristics |    |

| Table 28:  | FANC Signal Characteristics                 | 41 |

|            | FANP Signal Characteristics                 |    |

|            | Alert# Signal Characteristics               |    |

|            | FRU Addressing                              |    |

|            | LED Indicators                              |    |

# 1 Purpose

This document specifies a 48 VDC, single rail power supply for use in distributed schemes for server systems. The intent of the document is to define a power supply specification that enables the development of reliable, upgradable and extensible server components. Its intention is not to provide interoperability among different vendors of power supplies. Protection of producer and consumer investment is an important factor in the decision to implement this specification. Power supplies must meet all of the required features to be compliant to this specification.

# 2 Conceptual Overview

Servers using the power supply defined in this specification can be implemented either as modular or integrated systems. Modular systems are designed as multiple rack-mounted modules, with each module performing a specific function. Integrated systems are designed as one, integrated, rack-mountable server unit. Each of these system designs contains the following sub-systems:

- Electronics Bay (processor and memory)

- I/O Bay(s) (PCI I/O)

- Power Bay

- Peripheral bays

The processor/memory complex of the target server is generally designed to expand to a minimum of four processors; however, some server processor complexes may be expanded to up to eight or more processors. The memory expansion capacity and memory technology is sized to processor speed and a quantity of processors.

I/O functions are typically implemented with PCI add-in cards. In the integrated system design, the PCI cards are in the same module as the processor and memory. In the modular system, the PCI cards may be in a separate bay.

Integrated systems and modular systems both require additional peripheral expansion bays for sufficient mass storage capacity.

# 2.1 Distributed Power Architectural Overview

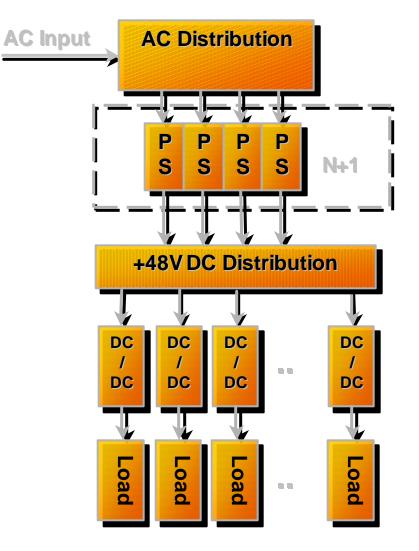

The goals of a distributed power system are to simplify the architecture of the power supply, and to move voltage conversion to the components, external to the power supply. A pictorial overview of the distributed power scheme is shown in Figure 1.

Figure 1: Distributed Power Scheme Overview

# 3 Definitions/Terms/Acronyms

| CFM                       | Cubic Feet per Minute (airflow).                                                                                                                                                               |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electronics Bay           | The volume and mechanical chassis to support the standard Electronics-Bay unit containing the processor, memory, and minimal I/O.                                                              |

| EMI                       | Electromagnetic Interference                                                                                                                                                                   |

| FRU                       | Field Replaceable Unit.                                                                                                                                                                        |

| IPMI                      | Intelligent Platform Management Interface. Refer to <a href="http://developer.intel.com/design/servers/ipmi/spec.htm">http://developer.intel.com/design/servers/ipmi/spec.htm</a> for detials. |

| I/O Bay                   | The volume and mechanical chassis to support the standard 'I/O-Bay' unit containing I/O expansion devices, such as HDDs, peripherals, or adapter cards                                         |

| Monotonically             | A waveform changes from one level to another in a steady fashion without negative slope or oscillation.                                                                                        |

| Noise                     | The periodic or random signals over frequency band of 0 Hz to 20 MHz.                                                                                                                          |

| PFC                       | Power Factor Corrected.                                                                                                                                                                        |

| Power Bay                 | The mechanical chassis supporting the power conversion from AC power to +48 VDC.                                                                                                               |

| Power Supply              | The volume, connector, and mechanical interface required in a chassis to support the standard power supply unit.                                                                               |

| PSU                       | Power Supply Unit.                                                                                                                                                                             |

| Ripple                    | The periodic or random signals over frequency band of 0 Hz to 20 MHz.                                                                                                                          |

| Rise Time                 | Rise time is defined as the time it takes any output voltage to rise from 10% to within regulation limits.                                                                                     |

| Sag                       | The condition where the AC line voltage drops below the nominal voltage conditions.                                                                                                            |

| SMBus                     | System Management Bus. This is a serial communication bus for low speed communication. Refer to <u>www.smbus.org</u> for details.                                                              |

| Surge                     | The condition where the AC line voltage rises above nominal voltage.                                                                                                                           |

| VSB or Standby<br>Voltage | An output voltage that is present whenever AC power is applied to the AC inputs of the supply.                                                                                                 |

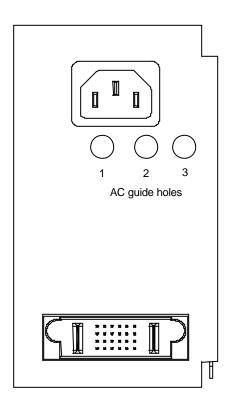

# 4 General

This specification describes the requirements for power supply that provides a minimum of 1200 W at 200-240 VAC. The AC input and DC output connectors are located on the side of the supply opposite the side where the handle is located. These connectors make contact with the system or power bay when the power supply is inserted. The power supply is designed to have parallel DC outputs, with active load sharing. Each power supply contains its own cooling fan(s). The power supply has a dual rating of 1200 W minimum over an input range of 180-264 VAC and 700 W minimum over an input range of 90-132 VAC.

# 5 Mechanical Overview

| STATUS   |  |

|----------|--|

| Required |  |

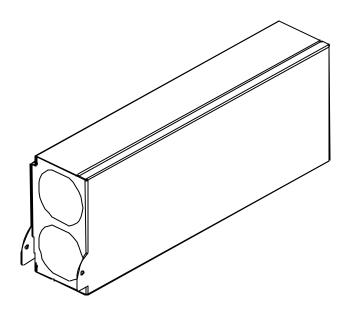

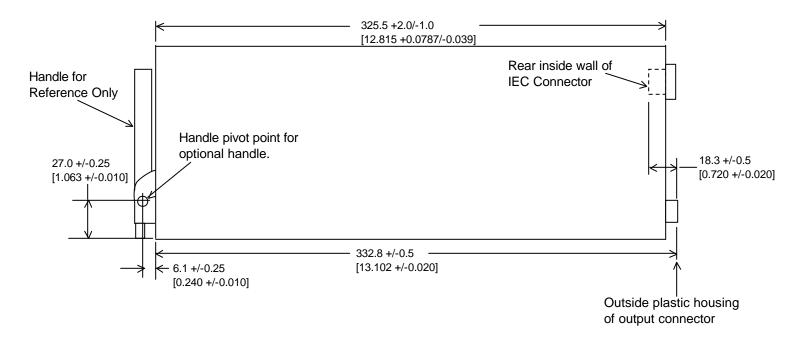

The physical form factors of the power supply are depicted in the following figures. The insertion and extraction force without the assistance of the handle must be less than 20 lb.

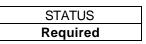

Figure 2: Form Factor

SSI

# DPS Power Supply Specification, V2.0

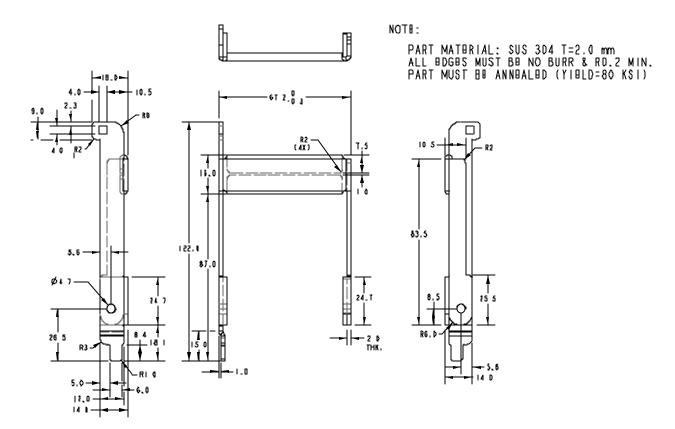

Figure 3: External Face

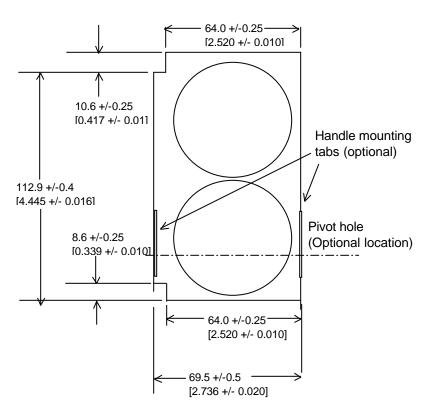

Figure 4: Side View

# 5.1 Connector Locations

The location of the DC output connector and AC inlet connector are shown in Figure 5. The location three guide holes are also shown. These holes provide a guide feature for mating the AC connector into the system or power bay. There must be clearance inside the power supply to allow a 1" guide pin to be inserted into these holes. These holes also provide keying for different versions of power supply that have different airflow directions. Refer to Section 5.3 for more description of airflow keying.

Figure 5: Interior Face

# 5.2 Handle and Retention Mechanism

| STATUS   |

|----------|

| Required |

The power supply must dock and undock into the power bay or system with less than 10 lb of insertion and extraction force when using the assistance of the power supply handle.

The retention method must hold the supply in the system during the specified shock and vibration tests without the power supply backing out of the system. The power supply retention feature must allow for functionality in the four possible orientations of the power supply. The retention mechanism must not require that a tool be used remove or insert the supply.

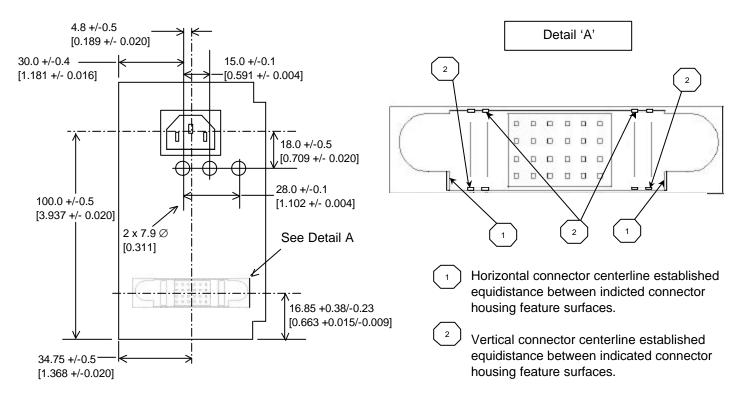

# 5.2.1 Handle/Retention Concept

| STATUS   |  |

|----------|--|

| Optional |  |

A concept drawing of an optional mechanism is shown in Figure 6.

Figure 6: Handle/Retention Mechanism

# 5.3 Power Supply Case Keying for Airflow

| STATUS   |  |

|----------|--|

| Required |  |

The case is keyed to guarantee that power supplies with the proper airflow direction are used in the correct systems and power bays. This is done by providing different locations for the AC guide holes. Refer to Figure 7 for location details of these holes.

| Keying Hole Location <sup>1</sup> | Side of Power Supply Air is Exhausted                                                                                              |  |  |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1 and 3                           | Internal Face                                                                                                                      |  |  |

| 1 and 2                           | External Face                                                                                                                      |  |  |

|                                   | Only two of the three positions are open to accept keying pins. The other must be plugged or not available to accept a keying pin. |  |  |

Figure 7: Airflow Keying

# 5.4 Airflow Requirements

| STATUS   |  |

|----------|--|

| Required |  |

The airflow direction is intake from the DC connector face and the air is exhausted on the handle face of the supply. An optional airflow direction is intake from the handle face and exhaust from the DC connector face. The power supply airflow requirements are shown in Figure 8. There are two fan performance P-Q curves shown ( $PQ_{high fan}$ ,  $PQ_{low}$  fan) which may be selected by the system via the FANC signal to the power supply. These P-Q curves are the airflow of the assembled fan and power supply. The power supply may override the FANC signal and operate the fan at HIGH speed if the conditions of the power supply exceed the description for  $Q_{low}$  in the table below. The minimum airflow required by the power supply for cooling ( $Q_{high}$ ,  $Q_{low}$ ) are shown in Table 1.  $Q_{high}$  and  $Q_{low}$  can be tested by applying back pressure or reducing fan RPM to obtain the needed airflow for testing. The maximum back pressure which a system can present to the power supply ( $PQ_{sys imp}$ ) is shown in Figure 8.

| ltem                   | Description                                                                                              | MIN                                         | MAX                                                   | Units                |

|------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------------------------------------------------|----------------------|

| $Q_{high}$             | Airflow through power supply;<br>max load, Tambient = 50 °C, 5000<br>ft elevation                        | 20                                          |                                                       | CFM                  |

| Q <sub>low</sub>       | Airflow through power supply;<br>max load, Tambient = 35 °C, 5000<br>ft elevation                        | 15                                          |                                                       | CFM                  |

| PQ <sub>high fan</sub> | Pressure vs airflow curve required<br>from power supply at HIGH fan<br>speed.                            | Refer to High<br>Speed curve in<br>Figure 8 |                                                       | inches H2O vs<br>CFM |

| PQ <sub>low fan</sub>  | Pressure vs. airflow curve required from power supply at LOW fan speed.                                  | Refer to Low<br>Speed curve in<br>Figure 8  |                                                       | Inches H2O vs<br>CFM |

| PQ <sub>sys_imp</sub>  | Pressure vs airflow curve<br>representing worst case<br>backpressure on the power supply<br>by a system. |                                             | Refer to Max<br>System Impedance<br>curve in Figure 8 | inches H2O vs<br>CFM |

Figure 8: Power Supply Airflow P-Q Curve

# 5.4.1 Optional Airflow Constructions

| STATUS   |  |

|----------|--|

| Optional |  |

The power supply's internal design provides the option to create two airflow directions. The fan can be mounted to draw air through the power supply with inlet air being pulled in through the DC connector face or the fan can be mounted to push air through the power supply with exhaust air being blown out the DC connector face. These are two optional power supply constructions. Power supplies will be keyed to guarantee the proper power supply airflow direction is used for each system design. The keying method is shown in Section 5.3.

# 5.5 Thermal Requirements

| STATUS   |  |

|----------|--|

| Required |  |

| ltem            | Description                                                                                                    | MIN | MAX      | Units   |

|-----------------|----------------------------------------------------------------------------------------------------------------|-----|----------|---------|

| T <sub>op</sub> | Operating temperature range.                                                                                   | 0   | 50       | °C      |

| $\Delta T_{ps}$ | Temperature rise from inlet air to outlet<br>air of power supply.<br>20 CFM, 1200 W output power, Sea<br>level |     | 20<br>27 | °C<br>℃ |

|                 | 15 CFM, 1200 W output power, Sea<br>level                                                                      |     |          |         |

#### Table 2: Thermal Requirements

|                     | DPS Power Supply Specification, V |     |    |    |

|---------------------|-----------------------------------|-----|----|----|

| T <sub>non-op</sub> | Nonoperating temperature range.   | -40 | 70 | °C |

The power supply must meet UL enclosure requirements for temperature rise limits. All sides of the power supply with exception to the air exhaust side, must be classified as "Handle, knobs, grips, etc. held for short periods of time only".

# 5.6 Acoustic Requirement

| STATUS   |

|----------|

| Required |

The power supply must run at LOW fan speed under the conditions defined for  $Q_{low}$  in Table 1. The power supply must have less than 41 dBA of sound pressure noise (L<sub>p</sub>) at any bystander microphone location when operating at LOW fan speed.

The test setup shall be as follows: The PSU is a desktop module with bystander locations only. The PSU is to be placed on a table 28 to 36 inches high with the position of four bystander microphones. The microphones will be 1 meter away, centered on each side, 1.5 meters high, as measured from the floor, and placed at a 30° down angle. The A-weighted (100 -10 kHz) sound pressure must be measured at the four bystander positions. Sound pressure is a measurement of the total noise at the specified microphone location in the room.

#### **AC Input Requirements** 6

| STATUS   |  |

|----------|--|

| Required |  |

The power supply shall incorporate universal power input with active power factor correction, which shall reduce line harmonics in accordance with the EN61000-3-2 and JEIDA MITI standards.

#### 6.1 AC Inlet Connector

| STATUS   |  |

|----------|--|

| Required |  |

The AC input connector is an IEC 320 C-14 power inlet.

#### 6.2 AC Input Specification

| STATUS<br>Required |  |

|--------------------|--|

| Required           |  |

|                    |  |

The power supply must operate within all specified limits over the following input voltage range. Harmonic distortion of up to 10% THD must not cause the power supply to go out of specified limits.

| Table 3: AC input voltage |                     |                         |                     |                      |           |

|---------------------------|---------------------|-------------------------|---------------------|----------------------|-----------|

| Parameter                 | MIN                 | Rated                   | MAX                 | MAX Input Current    | O/P Power |

| Vin                       | 90 V <sub>ms</sub>  | 100-120 V <sub>ms</sub> | 140 V <sub>ms</sub> | 10.0 A <sub>ms</sub> | 700 W     |

| Vin                       | 180 V <sub>ms</sub> | 200-240 V <sub>ms</sub> | 264 V <sub>ms</sub> | 9.0 A <sub>rms</sub> | 1200 W    |

| Vin Frequency             | 47 Hz               | 50/60 Hz                | 63 Hz               |                      |           |

Table 2: AC Input Voltage

Note: The Max Input Current shall scale with amount of output power. Example: For a power supply with 1400 W of output power at 200-240 V<sub>rms</sub>, the Max Input Current shall be 9.0 \* (1400/1200) = 10.5 A<sub>rms</sub>.

#### 6.3 Efficiency

| STATUS   |  |

|----------|--|

| Required |  |

|          |  |

The power supply will have a minimum efficiency of 80% at maximum load and 90 VAC.

The power supply will have a minimum efficiency of 85% at maximum load and 180 VAC.

#### 6.4 AC Multiple Phase Input Capability

Power supplies must be designed to enable power bay and system implementations that use multiple-phase AC input power. In this configuration, not all power supplies in a power bay are required to be on the same AC power phase.

# 6.5 AC Line Dropout

An AC line dropout is defined to be when the AC input drops to 0 VAC for one cycle or less of the AC input during any phase of the AC line. During an AC dropout the power supply must meet voltage regulation requirements (Table 10) over the rated load. An AC line dropout shall not cause any tripping of control signals or protection circuits. If the AC dropout lasts longer than one cycle of the AC line, then the power supply should recover and meet all turn on requirements. The power supply must meet the AC dropout requirement over rated AC voltages, frequencies, and output loading conditions. Any dropout of the AC line shall not cause damage to the power supply.

# 6.6 AC Brownout Requirement

| STATUS   |  |

|----------|--|

| Optional |  |

To meet the AC Brownout Requirements the optional ACOK<sup>#</sup> and ACRange signals must be implemented along with circuits external from the power supply. The circuits external from the power supply control the PSON<sup>#</sup> signal based upon the ACOK<sup>#</sup> signals received from the power supplies. When enough ACOK<sup>#</sup> signals are asserted from the power supplies, all power supplies are enabled via the PSON<sup>#</sup> signal. The ACRange signal enables the ability to meet the brownout requirement over the 200-240 VAC range, otherwise, it defaults to the 100-240 VAC range.

## AC Turn Off Requirement

The Power system must be able to return to normal power up state after a slow brownout condition. The brownout is tested in all valid redundant power system configurations. While the power system is operating at full rated DC load, the AC line voltage is reduced from 180 VAC/50 Hz to 0 VAC and 90 VAC/60 Hz to 0 VAC at a constant rate over a period of 30 minutes. The power is then reapplied at 180 VAC/50 Hz and 90 VAC/60 Hz. The system must return to a normal power up state.

## AC Turn On Requirement

The power system must be able to return to normal power up state after a slow recovery condition. The recovery is tested in all valid redundant power system configurations the system. With the test loads configured for maximum system DC output in resistive mode, the AC line voltage is increased from 0 VAC to 180 VAC/50 Hz and 0 VAC to 90 VAC/60 Hz at a constant rate over 30 minutes. The system must return to a normal power up state.

# 6.7 AC Line Fuse

| STATUS   |

|----------|

| Required |

The power supply shall have two line fuses, one for each side of the AC input. AC line fusing shall be acceptable for all safety agency requirements. AC inrush current shall not cause the AC line fuse to blow under any conditions. All protection circuits in the power supply shall not cause the AC fuse to blow unless a component in the power supply has failed. This includes DC output load short conditions.

# 6.8 AC Line Inrush

| STATUS   |  |

|----------|--|

| Required |  |

AC line inrush current shall not exceed 35 A peak for one-quarter or more of the AC cycle. The inrush current must not exceed the I<sup>2</sup>t curve shown in Figure 9. The inrush current must not exceed 100 A peak for any duration of time.

The power supply must meet the inrush requirements for any rated AC voltage, during turn on at any phase of AC voltage, during hot plug, during any AC dropout condition, over the specified temperature range ( $T_{op}$ ), and during AC power cycling. The AC power cycling test condition is defined as cycling the AC power off and back on five times after the power supply has been operating at maximum load and has reached thermal stability. The period between the five AC power cycles could anywhere between 1 ms to 1 s. The duration of the off time for each the power cycles could be anywhere between 1 ms and 1 s.

Figure 9: Inrush Limit

# 6.9 Maximum AC Leakage Current to Ground

| STATUS   |  |

|----------|--|

| Required |  |

The maximum leakage current to ground for each power supply is 0.75 mA when tested at 240 VAC.

# 6.10 AC Line Transient Specification

| STATUS   |  |

|----------|--|

| Required |  |

AC line transient conditions are defined as "sag" and "surge" conditions. Sag conditions also commonly referred to as "brownout"; these conditions are defined as the AC line voltage dropping below nominal voltage conditions. "Surge" is defined to refer to conditions when the AC line voltage rises above nominal voltage. The power supply shall meet the requirements under the following AC line sag and surge conditions.

| AC Line Sag        |      |                      |                   |                                               |  |

|--------------------|------|----------------------|-------------------|-----------------------------------------------|--|

| Duration           | Sag  | Operating AC Voltage | Line<br>Frequency | Performance Criteria                          |  |

| Continuous         | 10%  | Nominal AC Voltage   | 50/60 Hz          | No loss of function or performance            |  |

| 0 to 1 AC<br>Cycle | 100% | Nominal AC Voltages  | 50/60 Hz          | No loss of function or performance            |  |

| >1 AC cycles       | >10% | Nominal AC Voltages  | 50/60 Hz          | Loss of function acceptable, self recoverable |  |

## Table 4: AC Line Sag Transient Performance

| AC Line Surge   |     |                                  |                   |                                    |  |  |

|-----------------|-----|----------------------------------|-------------------|------------------------------------|--|--|

| Duration Surge  |     | Operating AC Voltage             | Line<br>Frequency | Performance Criteria               |  |  |

| Continuous      | 10% | Nominal AC Voltages              | 50/60 Hz          | No loss of function or performance |  |  |

| 0 to ½ AC cycle | 30% | mid-point of nominal AC Voltages | 50/60 Hz          | No loss of function or performance |  |  |

# 6.11 AC Line Fast Transient Specification

| STATUS   |  |

|----------|--|

| Required |  |

The power supply shall meet the *EN61000-4-5* directive and any additional requirements in *IEC1000-4-5:1995* and the Level 3 requirements for surge-withstand capability, with the following conditions and exceptions:

- These input transients must not cause any out-of-regulation conditions, such as overshoot and undershoot, nor must it cause any nuisance trips of any of the power supply protection circuits.

- The surge-withstand test must not produce damage to the power supply.

- The supply must meet surge-withstand test conditions under maximum and minimum DC-output load conditions.

# 7 DC Output Specification

The power supply must have a main 48 VDC output and a low current 12 VSB output. The 12 VSB output is always available when AC input power is applied to the power supply (with the exception of a fault condition that has opened the AC line fuse(s)). 12 VSB is used to power system components (i.e., server management) that must be available when the system is powered down.

# 7.1 DC Power Connector Requirements

| STATUS   |  |

|----------|--|

| Required |  |

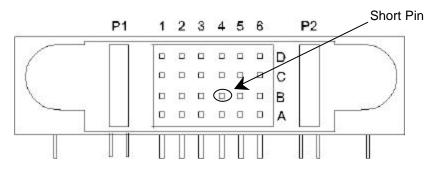

The DC connector shall have the pin-out illustrated in Table 7. The DC power connector is the Berg 51415-001 or equivalent. The connector is illustrated in Figure 10. The connector location on the power supply is shown in Figure 5.

# NOTE

Signals that can be defined as low true or high true use the following convention: signal<sup>#</sup> = low true

| Signal               | Description          | Signal            | Description           | Signal   | Description                    |  |

|----------------------|----------------------|-------------------|-----------------------|----------|--------------------------------|--|

| 48LS                 | 48 V load share bus  | PWOK              | Power OK output       | SCL      | I <sup>2</sup> C Clock signal  |  |

| 12 VSB               | 12 V standby output  | ACOK <sup>#</sup> | AC OK output          | SDA      | I <sup>2</sup> C Data signal   |  |

| 12 VSB<br>Return     | 12 V standby return  | ACRange           | AC input range select | A0       | I <sup>2</sup> C address bit 0 |  |

| PSON <sup>#</sup>    | Power enable input   | PSKILL            | Supply fast shutdown  | A1       | l <sup>2</sup> C address bit 1 |  |

| PRESENT <sup>#</sup> | Power supply present | FAIL              | Failure signal        | A2       | l <sup>2</sup> C address bit 2 |  |

| FANC                 | Fan control signal   | PRFL              | Predictive failure    | PSAlert# | Power supply alert             |  |

| FANP                 | Fan power input pin  |                   |                       |          |                                |  |

Table 6: Signal Descriptions

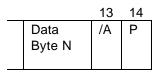

|   |           |                  | Juipui               | Conneo  |                     |          |      |

|---|-----------|------------------|----------------------|---------|---------------------|----------|------|

|   |           |                  | Signa                | al Pins |                     |          |      |

|   | 1         | 2                |                      | 3       | 4                   | 5        | 6    |

| D | 12 VSB    | 12 VSB<br>Return | 48LS                 |         | ACRange             | SCL      | A0   |

| С | 12 VSB    | 12 VSB<br>Return | ACOK <sup>#</sup>    |         | PRFL                | Reserved | A1   |

| В | 12 VSB    | 12 VSB<br>Return | PSON <sup>#</sup>    |         | PSKILL <sup>1</sup> | SDA      | A2   |

| А | FANP      | PSAlert#         | PRESENT <sup>#</sup> |         | PWOK                | FAIL     | FANC |

|   |           |                  | Power                | Blades  | i                   |          |      |

|   | P1        |                  |                      |         |                     | P2       |      |

|   | 48 VDC Re | turn             |                      |         |                     | 48 VDC   |      |

#### Table 7: Output Connector Pin-out

1. Pin B4 is shortened to allow the PSKill pin to shut down the power supply properly during hot swapping of the power supply.

Figure 10: DC Output Connector

# 7.2 DC Output Rating

| STATUS   |  |

|----------|--|

| Required |  |

The 48 VDC and 12 VSB outputs must meet ALL requirements over the loading and AC input conditions as shown in Table 8. The 12 VSB output must meet all requirements with the power supply operational (PSON = Low) or in standby mode (PSON = Open). When in standby mode the power supply fan must be OFF.

| Output | Low Load (Amps) | High Load (A) | Input Voltage (VAC) |

|--------|-----------------|---------------|---------------------|

| 48 VDC | 10% of Max      | 24            | 180 - 264 VAC       |

| 12 VSB | 0               | 4.0           | 180 - 264 VAC       |

| 48 VDC | 10% of Max      | 13.5          | 90 - 132 VAC        |

| 12 VSB | 0               | 4.0           | 90 - 132 VAC        |

## Table 8: DC Output Rating

The 48 VDC output shall have a peak output capacity 110% of maximum load. The duration of the peak current capacity shall be 10 s.

# 7.2.1 No Load Operation

| STATUS   |

|----------|

| 51A105   |

| Required |

The power supply operation at no load shall meet all requirements with the exception of the transient loading requirements.

# 7.3 Grounding

| STATUS   |  |

|----------|--|

| Required |  |

The 12 VSB Return must be connected to the power supply chassis and to earth ground of the AC inlet internally to the supply. All control signals are referenced to the 12 VSB Return (chassis ground). The 48 VDC Return and 48 VDC output must be isolated from the 12 VSB Return and 12 VSB output by greater than 10 k $\Omega$ . The resistance from chassis ground to either side of the 48 VDC output must be greater than 10 k $\Omega$ . The power supply must be able to operate within specified limits if a voltage of V<sub>CMop</sub> is applied at 48 VDC Return referenced to the 12 VSB Return (power supply chassis ground). If V<sub>CMop</sub> exceeds this range, the power supply may shut down, however, this must not damage the power supply. The power supply must not be damaged if a voltage of V<sub>CMfloat</sub> is applied at 48 VDC Return referenced to the 12 VSB Return (power supply chassis ground). The voltage at 48 VDC Return referenced to the 12 VSB Return (power supply chassis ground) must not exceed V<sub>CMfloat</sub> if the 48 VDC output is floating.

| Characteristic         | Description                                                                                                                                   | MIN    | MAX   |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|

| R <sub>isolation</sub> | Isolation from 12 VSB Return (chassis ground) to the 48 VDC Return.                                                                           | 10 kΩ  |       |

| V <sub>CMop</sub>      | Voltage applied to 48 VDC Return<br>referenced to 12 VSB Return. The<br>power supply must operate within all<br>specified limits.             | -1.0 V | 0 V   |

| V <sub>CMfloat</sub>   | Voltage applied between 48 VDC<br>Return and 12 VSB Return by an<br>external voltage. The supply must not<br>be damaged under this condition. | -50 V  | +50 V |

|                        | Voltage present between 48 VDC<br>Return and 12 VSB Return during<br>normal operation with the 48 VDC<br>Return floating.                     |        |       |

Table 9: 48 VDC Isolation Requirements

# 7.4 Regulation

| STATUS   |  |

|----------|--|

| Required |  |

The 48 VDC and 12 VSB outputs do not require remote sensing. All voltage regulation measurements are made at the output connector of the power supply. These limits do not include the peak-peak ripple/noise specified in Section 7.7. The power supply must hold regulation limits under all operating conditions (AC line, transient loading, and output loading) as shown in Table 10.

| Output | MIN   | NOM   | MAX    | Units | % Reg |

|--------|-------|-------|--------|-------|-------|

| 48 VDC | +45.6 | +48.0 | +50.4  | Volts | +/-5% |

| 12 VSB | +12.0 | +12.5 | +13.00 | Volts | +/-4% |

# Table 10: DC Output Regulation

# 7.5 Transient Loading

| STATUS   |  |

|----------|--|

| Required |  |

The power supply must operate within specified limits and meet regulation requirements over the following transient loading conditions. The transient load can occur anywhere within the load range of the power supply. This is tested with no additional bulk capacitance.

| Table 11: Transient Response |             |           |                                      |

|------------------------------|-------------|-----------|--------------------------------------|

| Output                       | Step Size   | Slew Rate | Number of Power Supplies in Parallel |

| 48 VDC                       | 50% of max  | 0.25 A/μs | 1                                    |

| 48 VDC                       | 50% of max  | 0.50 A/µs | 2                                    |

| 48 VDC                       | 50% of max  | 0.75 A/μs | 3                                    |

| 48 VDC                       | 50% of max  | 1.0 A/μs  | 4                                    |

| 48 VDC                       | 50% of max  | 1.0 A/μs  | 5                                    |

| 48 VDC                       | 50% of max  | 1.0 A/μs  | 6                                    |

| 12 VSB                       | 100% of max | 1.0 A/μs  | 1                                    |

# 7.6 Capacitive Load

| STATUS   |  |

|----------|--|

| Required |  |

The power supply must operate within specified limits over a capacitive load range define in Table 12.

|        | Table 12: Capacitive Loading |           |                                      |  |

|--------|------------------------------|-----------|--------------------------------------|--|

| Output | MIN                          | MAX       | Number of Power Supplies in Parallel |  |

| 48 VDC | 0 μF                         | 10,000 μF | 1                                    |  |

| 48 VDC | 0 μF                         | 20,000 μF | 2                                    |  |

| 48 VDC | 0 μF                         | 30,000 μF | 3                                    |  |

| 48 VDC | 0 μF                         | 40,000 μF | 4                                    |  |

| 48 VDC | 0 μF                         | 50,000 μF | 5                                    |  |

| 48 VDC | 0 μF                         | 60,000 μF | 6                                    |  |

#### 7.7 **Ripple and Noise**

Ripple and noise are measured with 0.1 µF of ceramic capacitance and 10 µF of tantalum capacitance on each of the power supply outputs. These capacitors are located at the power supply output connector. The ripple and noise requirements shall be met over all load ranges and AC line voltages with one to six power supplies in parallel operation. The output noise requirements apply over a 0 Hz to 20 MHz bandwidth. These requirements are specified in Table 13.

| Table 13: Ripple and Noise |                          |  |  |  |

|----------------------------|--------------------------|--|--|--|

| Output                     | Maximum Ripple and Noise |  |  |  |

| 48 VDC                     | 480 mVp-p                |  |  |  |

| 12 VSB                     | 120 mVp-p                |  |  |  |

#### 7.8 12 VSB

| STATUS   |  |

|----------|--|

| Required |  |

12 VSB is a standby voltage that may be used to power circuits that require power during the powered-down state of all power rails. 12 VSB is required for the implementation of PSON<sup>#</sup> and other system circuits that must stay powered when the system is turned off.

#### 7.9 Hot Swap Requirement

| STATUS   |  |

|----------|--|

| Required |  |

Hot swapping a power supply is the process of inserting and extracting a power supply from an operating power system. During this process the output voltages shall remain within the limits specified in Table 10 with the capacitive load specified Table 12. The hot swap test must be conducted when the system is operating under both static and dynamic conditions. The power supply can be hot swapped by the following methods:

- Up to four power supplies may be on a single AC line. Extraction: The AC power will be disconnected from the power supply as the power supply is being extracted from the system. This could occur in standby mode or powered on mode. Insertion: The AC power will be connected to the power supply as the supply is inserted into the system and the supply will power on into standby mode or powered on mode.

- Server management turning on the hot swapped power supply. Extraction: Server management turns off only one of the power supplies via the PSON<sup>#</sup> signal, then the power supply is removed from the system. Insertion: Power supply is inserted into the system, server management looks for power supply, depending upon the state of the system (on or off), the system then turns on the power supply via the PSON<sup>#</sup> signal or goes to standby mode operation.

Many variations of the above are possible. Supplies need to be compatible with these different variations. In general, a failed (off by internal latch or external control) supply may be removed, then replaced with a good power supply, however, hot swap needs to work with operational as well as failed power supplies. The newly inserted power supply may get turned on by inserting the supply into the system or by system management recognizing an inserted supply and explicitly turning it on.

# 7.9.1 Output Isolation

All outputs must have an isolating device to isolate the power supply from the system power during a power supply failure or during a hot swap operation. This device must be located in the power supply. This device can be an or'ing diode or functional equivalent.

# 7.10 Timing Requirements

| STATUS   |  |

|----------|--|

| Required |  |

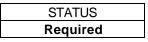

These are the timing requirements for single power supply operation. Timing is defined for turn on and turn off of the power supply. The output voltage must rise from 10% to within regulation limits ( $T_{vout\_rise}$ ) within 5 to 300 ms. Outputs must rise monotonically. The timing of signals and power are specified in Table 14 and described in Figure 11.

| ltem                   | Description                                                                                                     | MIN | MAX  | Units |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------|-----|------|-------|--|

| T <sub>vout_rise</sub> | Output voltage rise time from each main output.                                                                 | 5   | 300  | ms    |  |

| $T_{sb\_on\_delay}$    | Delay from AC being applied to 12 VSB being within regulation.                                                  |     | 1500 | ms    |  |

| $T_{ac\_on\_delay}$    | Delay from AC being applied to all output voltages being within regulation.                                     |     | 2500 | ms    |  |

| $T_{vout\_holdup}$     | Time all output voltages, including 12 VSB, stay within regulation after loss of AC.                            | 21  |      | ms    |  |

| $T_{pwok\_holdup}$     | Delay from loss of AC to deassertion of<br>PWOK                                                                 | 20  |      | ms    |  |

| $T_{pson\_on\_delay}$  | Delay from PSON <sup>#</sup> active to output voltages within regulation limits.                                | 5   | 400  | ms    |  |

| T <sub>pson_pwok</sub> | Delay from PSON <sup>#</sup> deactive to PWOK being deasserted.                                                 |     | 50   | ms    |  |

| $T_{acok\_delay}$      | Delay from loss of AC input to deassertion of ACOK#.                                                            | 20  |      | ms    |  |

| T <sub>pwok_on</sub>   | Delay from output voltages within regulation limits to PWOK asserted at turn on.                                | 100 | 1000 | ms    |  |

| T <sub>pwok_off</sub>  | Delay from PWOK deasserted to 48 VDC or 12 VSB dropping out of regulation limits.                               | 1   |      | ms    |  |

| T <sub>pwok_low</sub>  | Duration of PWOK being in the deasserted state during an off/on cycle using AC or the PSON <sup>#</sup> signal. | 100 |      | ms    |  |

| T <sub>sb_vout</sub>   | Delay from 12 VSB being in regulation to 48 VDC being in regulation at AC turn on.                              | 50  | 1000 | ms    |  |

## Table 14: Turn On/Off Timing

DPS Power Supply Specification, V2.0

Figure 11: Turn On/Off Timing

# 7.11 Forced Load Sharing

| STATUS   |  |

|----------|--|

| Required |  |

The 48 VDC output shall have forced load sharing. The output must share within 6.7% at full load, as shown in the example below and in Table 15. All current sharing functions are implemented internal to the power supply by making use of the 48LS signal. The system connects the 48LS signals between the power supplies. The supplies must be able to load share with up to six power supplies in parallel and operate in a hot swap/redundant n+1 configuration where n=1, 2, 3, 4, and 5.

Example: Power supply #1 = 15.0 A Power supply #2 > 14.0 A and < 16.0 A

| Number<br>of Power | System Maximum Current (Amps) for Non-redundant Power<br>Supply Configurations |             |                             | System Maximum Power (W) |             |  |

|--------------------|--------------------------------------------------------------------------------|-------------|-----------------------------|--------------------------|-------------|--|

| Supplies           | 100-120 VAC                                                                    | 200-240 VAC | 100-120 VAC and 200-240 VAC | 100-120 VAC              | 200-240 VAC |  |

|                    | 48 VDC                                                                         | 48 VDC      | 12 VSB                      |                          |             |  |

| 1                  | 13.5                                                                           | 24          | 4                           | 700                      | 1200        |  |

| 2                  | 26                                                                             | 46          | 8                           | 1350                     | 2300        |  |

| 3                  | 38                                                                             | 68          | 12                          | 2000                     | 3400        |  |

| 4                  | 51                                                                             | 91          | 16                          | 2650                     | 4550        |  |

| 5                  | 63                                                                             | 113         | 20                          | 3300                     | 5650        |  |

| 6                  | 76                                                                             | 135         | 24                          | 3950                     | 6750        |  |

Table 15: System Load

# 7.11.1 Load Sharing Control

| STATUS   |  |

|----------|--|

| Required |  |

The power supplies load share by using a single load share bus signal connected between the power supplies for the 48 VDC output. If the load sharing is disabled by shorting the load share bus to ground, the power system must continue to operate within regulation limits for loads less than or equal to one power supply. The failure of a power supply should not effect the load sharing or output voltages of the other supplies still operating. The power supplies must be able to load share with up to 100 mV of drop between the grounds of the different power supply outputs.

# 7.11.2 Load Share Signal Characteristics

| STATUS      |  |

|-------------|--|

| Recommended |  |

The load share signal provides both output current information and the load sharing function. The characteristics of the load share signal is defined below in Table 16.

| ltem                                                  | Description                                                                                                                           | MIN | NOM                     | MAX | Units |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------|-----|-------|

| V <sub>share</sub> ; I <sub>out</sub> =max            | Voltage of load share bus at specified max output current.                                                                            |     | 8                       |     | V     |

| $\Delta V_{share} / \Delta I_{out}$ ; $I_{out} > 1$ A | Slope of load share bus voltage with changing load.                                                                                   |     | 8 / I <sub>outmax</sub> |     | V / A |

| $I_{share}$ sink; $V_{share}$ =8 V                    | Amount of current the load share bus output from each power supply sinks.                                                             |     |                         | 0.5 | mA    |

| I <sub>share</sub> source; V <sub>share</sub> =8<br>V | Amount of current the load share bus output from each power supply sources.                                                           | 4.0 |                         |     | mA    |

| T <sub>share</sub> ; I <sub>out</sub> =max            | Delay from output voltages in regulation to<br>load sharing active with maximum load of<br>one power supply and two power supplies in |     |                         | 100 | ms    |

| Table 16: | Load Share | Bus Output | Characteristic |

|-----------|------------|------------|----------------|

| DPS Power Supply Specification, |  |  | ation, V2.0 |  |

|---------------------------------|--|--|-------------|--|

| parallel.                       |  |  |             |  |

SS

# 7.11.3 Standby Load Sharing

| STATUS   |  |

|----------|--|

| Required |  |

The 12 VSB output must be able to provide an additional 4.0 A of output current for each additional power supply added in parallel. Each power supply in the system will deliver current up to the current limit point, as stated in Section 8.2. At this point the power supply will go into constant current mode and allow other power supplies in the system to deliver additional standby current.

| Table 17: Standby Load Sharing |                     |                            |

|--------------------------------|---------------------|----------------------------|

| Number of S                    | upplies in Parallel | 12 VSB Load                |

|                                | 1                   | 4.0 A                      |

|                                | 2                   | 8.0 A                      |

|                                | 3                   | 12.0 A                     |

|                                | 4                   | 16.0 A                     |

|                                | 5                   | 20.0 A                     |

|                                | 6                   | 24.0 A                     |

|                                | 3<br>4<br>5         | 12.0 A<br>16.0 A<br>20.0 A |

# 8 Protection Circuits

| STATUS   |  |

|----------|--|

| Required |  |

Protection circuits inside the power supply shall cause only the power supply's main outputs to shutdown. The 12 VSB output shall remain powered on if the failure does not involve this output. When a protection circuit shuts down the power supply both the FAIL LED and the FAIL signal will be activated. If the power supply latches off due to a protection circuit tripping, an AC cycle OFF for 15 s and a PSON<sup>#</sup> cycle HIGH for 1 s must be able to reset the power supply.

# 8.1 Over-voltage Protection

| STATUS   |

|----------|

| Required |

The power supply's over voltage protection shall be locally sensed. The power supply shall shutdown in a latch off mode after an over voltage condition. This latch can be cleared by toggling the PSON<sup>#</sup> signal or by an AC power interruption. Table 18 contains the over voltage limit. The values are measured at the output of the Power Supply DC connector.

| Table 18: Over-voltage Protection Requirements |     |       |

|------------------------------------------------|-----|-------|

| Output                                         | MAX | Units |

| 48 VDC                                         | 55  | volts |

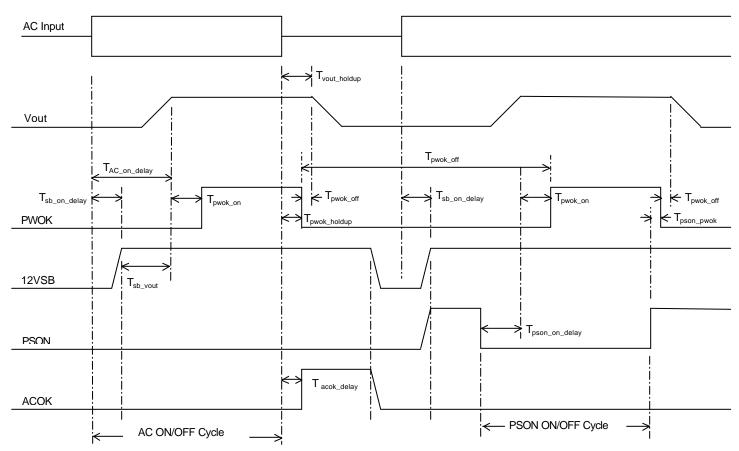

# 8.2 Over-current / Short Circuit Protection

|          | STATUS   |  |

|----------|----------|--|

| Required | Required |  |

The power supply shall have current limit to prevent the 48 VDC output from exceeding the value shown in Table 19. The current limiting shall be of the constant current type for both the 48 VDC and 12 VSB outputs. When in current limit for loads less then 600% of maximum, the output current must not decrease as the load resistance decreases.

The over current limit level for the 48 VDC output shall be maintained for a period of 2.5 s minimum and 6 s maximum. For loads greater than 600% of maximum rating on the 48 VDC output the power supply may shutdown in less than 2600 ms.

The over current limit for the 12 VSB output shall be maintained indefinitely, without shutting down the power supply, for loads less than 24 A. For loads greater than 24 A on the 12 VSB output the power supply may shutdown in less than 1500 ms.

After this current limit time for the 48 VDC output the power supply shall latch off. If the load on the 12 VSB output is greater than 24 A the power supply may latch off to protect the power supply. The latch will be cleared by toggling the PSON<sup>#</sup> signal or by an AC power interruption. The power supply shall not be damaged from repeated power cycling in this condition.

| Table 19: Over Current Protection |                                |

|-----------------------------------|--------------------------------|

| VOLTAGE                           | OVER CURRENT LIMIT(lout limit) |

| 48 VDC                            | 110% minimum; 150% maximum     |

| 12 VSB                            | 100% minimum; 125% maximum     |

Figure 12: Current Limit Characteristic

# 8.3 Thermal Protection

| STATUS   |  |

|----------|--|

| Required |  |

The power supply will be protected against over temperature conditions caused by loss of fan cooling or excessive ambient temperature. In an OTP condition the PSU will be shutdown with the exception of the 12 VSB output. When the power supply temperature drops to within specified limits, the power supply shall restore power automatically. The OTP circuit must have built in hysteresis such that the power supply will not oscillate on and off due to temperature recovering condition. The power supply shall alert the system of the OTP condition via the power supply FAIL signal and the FAIL LED indicator.

# 9 Control and Indicator Functions

The following sections define the input and output signals from the power supply. Signals that can be defined as low true or high true use the following convention:  $signal^{#} = low$  true.

# 9.1 **PSON<sup>#</sup>** (Power Supply Enable)

| STATUS   |  |

|----------|--|

| Required |  |

The PSON<sup>#</sup> signal is required to remotely turn on/off the power supply. PSON<sup>#</sup> is an active low signal that turns on the 48 VDC power rail. When this signal is not pulled low by the system, or left open, the 48 VDC output turns off and the 12 VSB output remains on. The power supply is in standby mode when PSON<sup>#</sup> is not pulled low or left open. When the power supply is in standby mode the power supply fan must be OFF. PSON<sup>#</sup> is pulled to a bias voltage by a pull-up resistor internal to the power supply. This bias voltage shall be present when the power supply shuts down due to any protection circuits or when the 12 VSB goes into current limit. Refer to Figure 11 for the timing diagram.

| Table 20: PSON Signal Characteristic           |                                                                                  |                  |

|------------------------------------------------|----------------------------------------------------------------------------------|------------------|

| Signal Type                                    | Accepts an open collecto<br>system. Pull-up to house<br>independent of 12 VSB lo | ekeeping voltage |

| PSON <sup>#</sup> = Low, PSKILL = Low          | C                                                                                | N                |

| PSON <sup>#</sup> = Open, PSKILL = Low or Open | OFF                                                                              |                  |

| PSON <sup>#</sup> = Low, PSKILL = Open         | OFF                                                                              |                  |

|                                                | MIN                                                                              | MAX              |

| Logic level low (power supply ON)              | 0 V                                                                              | 1.0 V            |

| Logic level high (power supply OFF)            | 2.0 V 5.25 V                                                                     |                  |

| Source current, Vpson = low                    |                                                                                  | 1 mA             |

| Power up delay: T <sub>pson_on_delay</sub>     | 5 ms                                                                             | 400 ms           |

| PWOK delay: T pson_pwok                        |                                                                                  | 50 ms            |

Table 20: PSON<sup>#</sup> Signal Characteristic

# 9.2 PSKill

| STATUS   |  |

|----------|--|

| Required |  |

The purpose of the PSKill pin is to allow for hot swapping of the power supply. The PSKill pin on the power supply is shorter than the other signal pins. When a power supply is operating in parallel with other power supplies and then extracted from the system, the PSKill pin will quickly turn off the power supply and prevent arching of the DC output contacts. The DC output contacts must not arch under this condition. T<sub>PSKill</sub> (shown below in Table 21) is the minimum time delay from the PSKill pin unmating to when the power pins unmate. The power supply must discharge its output inductor within this time from the unmating of the PSKill pin. When the PSKill signal is not pulled down or left opened (power supply is extracting from the system), the power supply should shut down regardless of the condition of the PSON<sup>#</sup> signal. The mating pin of this signal in the system should be tied to ground. Internal to the power supply, the PSKill pin, the power supply will be allowed to turn on via the PSON<sup>#</sup> signal. A logic LOW on this pin by itself should not turn on the power supply will be.

| Signal Type (Input Signal to Supply)                                                       | Accepts a ground input from the system. Pull-up to VSB located in the power supply. |        |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------|

| PSKILL = Low, PSON <sup>#</sup> = Low                                                      | ON                                                                                  |        |

| PSKILL = Open, PSON <sup>#</sup> = Low or Open                                             | OFF                                                                                 |        |

| PSKILL = Low, PSON <sup>#</sup> = Open                                                     | OFF                                                                                 |        |

|                                                                                            | MIN                                                                                 | MAX    |

| Logic level low (power supply ON)                                                          | 0 V                                                                                 | 1.0 V  |

| Logic level high (power supply OFF)                                                        | 2.0 V                                                                               | 5.25 V |

| Source current, VOSKill = low                                                              |                                                                                     | 4 mA   |

| Delay from PSKill = High to power<br>supply turned off (T <sub>PSKill</sub> ) <sup>1</sup> |                                                                                     | 100 μs |

1. T<sub>PSKill</sub> is the time from the PSKill signal deasserting HIGH to the power supply's output inductor discharging.

# 9.3 AC Input Range Setting (ACRange)

| STATUS   |  |

|----------|--|

| Optional |  |

ACRange allows the power supply to meeting the AC Brownout requirement over the 200-240 VAC input voltage range. Refer to Table 22. It communicates the AC input voltage range the power supply is operating at by setting the trip point for the ACOK<sup>#</sup> signal. If the signal is open, the power supply defaults to the 100-240 VAC input range. If the signal is pulled low, the range is set to 200-240 VAC.

| Signal Type                              | Accepts an open collector/drain input from the system. Pull-up to VSB located in the system. |        |  |  |

|------------------------------------------|----------------------------------------------------------------------------------------------|--------|--|--|

| ACRange = Low                            | 200-240 VAC                                                                                  |        |  |  |

| ACRange = Open (Default)                 | 100-240 VAC                                                                                  |        |  |  |

|                                          | MIN                                                                                          | MAX    |  |  |

| Logic level low voltage<br>(200-240 VAC) | 0 V                                                                                          | 1.0 V  |  |  |

| Logic level high (100-240 VAC)           | 2.0 V                                                                                        | 5.25 V |  |  |

| Source current, Vacrange = low           |                                                                                              | 4 mA   |  |  |

| Tabla | 22. | ACDanaa | Cianal | Characteristic |

|-------|-----|---------|--------|----------------|

| rable |     | AURANUE | SIGHAL | Characteristic |

# 9.4 ACOK<sup>#</sup> Signal

| STATUS   |  |

|----------|--|

| Optional |  |

ACOK<sup>#</sup> allows the power supply to meet the AC Brownout requirement with multiple power supplies in parallel. Refer to Table 23. This signal is pulled LOW when the AC input voltage has reached the minimum level defined by the ACRange signal. The characteristic of the ACOK<sup>#</sup> signal is shown in Table 23. Refer to Figure 11 for timing diagram.

The purpose of this signal is to synchronize the power on timing of multiple power supplies within the system. The system will monitor the ACOK<sup>#</sup> signals. When enough ACOK<sup>#</sup> signals are active to allow the system to be powered on, the system will activate the PSON<sup>#</sup> signals to all power supplies.

| Table 23: A                                      | COK <sup>#</sup> Signal Characterist                                                 | ics     |

|--------------------------------------------------|--------------------------------------------------------------------------------------|---------|

| Signal Type                                      | Open collector/drain output from power supply. Pull-<br>up to VSB located in system. |         |

| ACOK <sup>#</sup> = Low                          |                                                                                      | AC OK   |

| ACOK <sup>#</sup> = High                         |                                                                                      | AC Low  |

|                                                  | MIN                                                                                  | MAX     |

| Logic level low voltage, lsink=4 mA              | 0 V                                                                                  | 0.4 V   |

| Logic level high voltage, lsink=50 mA            |                                                                                      | 5.25 V  |

| Sink current, ACOK <sup>#</sup> = low            |                                                                                      | 4 mA    |

| Sink current, ACOK <sup>#</sup> = high           |                                                                                      | 50 µA   |

| ACOK <sup>#</sup> trip point for 200-240 VAC     |                                                                                      | 175 VAC |

| ACOK <sup>#</sup> trip point for 100-240 VAC     |                                                                                      | 85 VAC  |

| ACOK <sup>#</sup> Delay: T <sub>acok_delay</sub> | 20 ms                                                                                |         |

| ACOK <sup>#</sup> rise and fall time             |                                                                                      | 100 μs  |

## 9.5 PWOK (Power Good)

| STATUS   |  |

|----------|--|

| Required |  |

PWOK is a power good signal and will be pulled HIGH by the power supply to indicate that all the outputs are above the regulation limits of the power supply. When any output voltage falls below regulation limits or when AC power has been removed for a time sufficiently long so that power supply operation is no longer guaranteed, PWOK will be deasserted to a LOW state. See Figure 11 for a representation of the timing characteristics of PWOK. The start of the PWOK delay time shall be inhibited as long as any power supply's 48 VDC output is in current limit or the 12 VSB output is below the regulation limit.

|                                          |                                                                                                                    | 5       |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------|

| Signal Type                              | Open collector/drain output from power supply   Pull-up to VSB located power supply.   Power Good   Power Not Good |         |

| PWOK = High                              |                                                                                                                    |         |