# **OCTANE** Technical Report

Silicon Graphics, Inc.

ANY DUPLICATION, MODIFICATION, DISTRIBUTION, PUBLIC PERFORMANCE, OR PUBLIC DISPLAY OF THIS DOCUMENT WITHOUT THE EXPRESS WRITTEN CONSENT OF SILICON GRAPHICS, INC. IS STRICTLY PROHIBITED. THE RECEIPT OR POSSESSION OF THIS DOCUMENT DOES NOT CONVEY ANY RIGHTS TO REPRODUCE, DISCLOSE OR DISTRIBUTE ITS CONTENTS, OR TO MANUFACTURE, USE, OR SELL ANYTHING THAT IT MAY DESCRIBE, IN WHOLE OR IN PART.

Copyright © 1997 Silicon Graphics, Inc. ALL RIGHTS RESERVED

# Table of Contents

| Section | 1 Intro | oduction1-1                              |

|---------|---------|------------------------------------------|

| 1.1     | Mar     | nufacturing1-3                           |

|         | 1.1.1   | Industrial Design1-3                     |

|         | 1.1.2   | CAD/CAM Solid Modeling1-4                |

|         | 1.1.3   | Analysis1-5                              |

|         | 1.1.4   | Digital Prototyping1-6                   |

| 1.2     | Ente    | ertainment                               |

|         | 1.2.1   | 3D Animation1-8                          |

|         | 1.2.2   | Film/Video/Audio1-9                      |

|         |         | Publishing1-10                           |

| 1.3     | Def     | ense/SImulation                          |

|         | 1.3.1   | Defense Imaging1-12                      |

|         | 1.3.2   | Visual Simulation                        |

|         | 1.3.3   | Geographic Information Systems (GIS)1-14 |

| 1.4     |         | ences1-15                                |

|         | 1.4.1   | Oil and Gas1-15                          |

|         | 1.4.2   | Chemistry1-15                            |

|         | 1.4.3   | Medical Imaging1-17                      |

| Section | 2 Syst  | em Architecture                          |

| 2.1     |         | hitectural Overview                      |

| 2.1     |         | Bus Bandwidth and Frequency              |

|         |         | OCTANE Board Layout                      |

|         |         | Packet Switching                         |

|         |         | Unfair Arbitration                       |

|         |         | Guaranteed Bandwidth and Latency2-5      |

|         | 2.1.6   | Data Transfer Types                      |

|         |         | Link Level Protocol                      |

|         |         | System Modularity                        |

| 2.2     |         | 0000 Processor                           |

|         |         | Register Renaming                        |

|         | 2.2.2   | Out-of-Order Execution                   |

|         | 2.2.3   | Non-Blocking Caches                      |

|         | 2.2.4   | Branch Prediction                        |

|         | 2.2.5   | Primary Data Cache2-11                   |

|         | 2.2.6   |                                          |

|         | 2.2.7   | Secondary Cache Interface2-11            |

|         | 2.2.8   | Instruction Queues2-11                   |

|         | 2.2.9   | System Interface2-12                     |

| 2.3     | Sys     | tem ASICs                                |

|         |         | Crossbow ASIC2-12                        |

|         |         | Heart ASIC2-15                           |

|         | 2.3.3   | Bridge ASIC2-19                          |

|               | nory System                               |         |

|---------------|-------------------------------------------|---------|

|               | Synchronous DRAMs                         |         |

| 2.4.2         | Memory Data Integrity                     | 2-24    |

| 2.5 I/O       | Subsystem                                 |         |

| 2.5.1         | SCSI Interface                            | 2-26    |

| 2.5.2         | Keyboard and Mouse                        | 2-27    |

| 2.5.3         | Ethernet Interface                        | 2-28    |

|               | Serial Port Interface                     |         |

|               | Parallel Port Interface                   |         |

|               |                                           |         |

|               | io Architecture                           |         |

|               | lio System                                |         |

|               | Software Compatibility                    |         |

|               | Synchronization                           |         |

|               | Scalability                               |         |

|               | Architectural Overview                    |         |

|               | Audio Configurations                      |         |

|               | The RAD ASIC                              |         |

| 3.1.7         | Standard Audio Peripherals                | 3-11    |

| Section 4 Gra | phics Architecture                        | 4.1     |

|               |                                           |         |

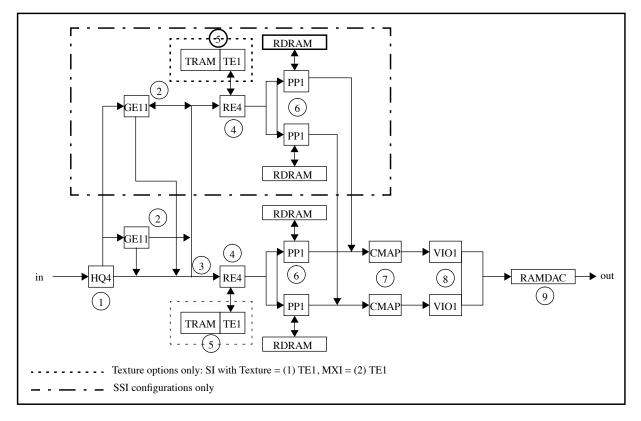

|               | phics Configurations                      |         |

|               | Solid Impact (SI)                         |         |

|               | Solid Impact with Texture Option          |         |

|               | Super Solid Impact (SSI)                  |         |

|               | Maximum Impact Option (MXI)               |         |

|               | phics Subsystem Components                |         |

|               | HQ4 - Bus Interface ASIC                  |         |

|               | GE11 - Geometry Engine ASIC               |         |

|               | RE4 - Raster Engine                       |         |

|               | TE1 - Texture Engine                      |         |

|               | TRAM - Texture RAM                        |         |

| 4.2.6         | HRBE - High Resolution Back End Circuitry | 4-11    |

| 4.3 Gra       | phics Data Flow                           | 4-11    |

| 4.4 OC        | TANE Graphics Features                    | 4-13    |

| 4.4.1         | MicroPixel Sub-Pixel Positioning          | 4-13    |

| 4.4.2         | Blending                                  | 4-13    |

| 4.4.3         | Point Anti-Aliasing                       | 4-14    |

|               | Line Anti-Aliasing                        |         |

|               | Accumulation Buffer                       |         |

|               | Lighting Features                         |         |

|               | Local Light and Viewer Positioning        |         |

|               | Atmospheric Effects                       |         |

|               | Texture Mapping                           |         |

|               | ) Stencil Planes                          |         |

|               | Arbitrary Clipping Planes                 |         |

|               | Pixel Read, Write, and Copy               |         |

|               | B Imaging Operations                      |         |

|               | Standard Visuals                          |         |

|               | Detail Texture                            |         |

|               | 6 Pixel Textures                          |         |

| 4.4.10        | 1 1A01 1 0Aturos                          | ······+ |

|         | 4.4.17 Pixel Buffers                           | 4-24 |

|---------|------------------------------------------------|------|

|         | 4.4.18 Framebuffer Configuration (FBConfig)    | 4-24 |

|         | 4.4.19 Video Texturing                         | 4-24 |

|         | 4.4.20 Other OpenGL Extensions                 | 4-24 |

| Section | 5 Software Environment                         | 5-1  |

| 5.1     | Operating System                               |      |

|         | 5.1.1 Scalability                              |      |

|         | 5.1.2 Compatibility                            |      |

|         | 5.1.3 Availability                             |      |

|         | 5.1.4 Scheduler                                |      |

|         | 5.1.5 File Systems                             |      |

|         | 5.1.6 Memory Management                        |      |

| 5.2     |                                                |      |

| J.2     | 5.2.1 IRIX/Motif                               |      |

|         | 5.2.2 Display PostScript                       |      |

|         | 5.2.3 X11 and the OpenGL                       |      |

|         | 5.2.4 OpenGL                                   |      |

|         | 5.2.5 Open Inventor                            |      |

|         | 5.2.6 IrisGLTM on OCTANE                       |      |

|         | 5.2.7 CASEVision                               |      |

|         | 5.2.8 Compilers and Standard Development Tools |      |

|         | 5.2.9 Image Processing Library                 |      |

|         | 5.2.10 Digital Media Libraries                 |      |

|         | 5.2.11 IRIS Performer                          |      |

| 5.3     |                                                |      |

| 5.5     | 5.3.1 IRIS InSight <sup>™</sup> Viewer         |      |

|         | 5.3.2 IRIS Showcase <sup>TM</sup> $3.3$        |      |

|         | 5.3.3 Media Tools                              |      |

|         | 5.3.4 Digital Media Clip Library               |      |

| 5.4     |                                                |      |

|         |                                                |      |

| Section | 6 Specifications                               |      |

| 6.1     |                                                |      |

|         | 6.1.1 Audio Ports                              |      |

|         | 6.1.2 SCSI Port                                |      |

|         | 6.1.3 Ethernet 10 Base-T/100 Base-T Port       |      |

|         | 6.1.4 Parallel Port                            |      |

|         | 6.1.5 Keyboard and Mouse Ports                 |      |

|         | 6.1.6 Serial Ports                             | 6-9  |

| 6.2     | 1                                              |      |

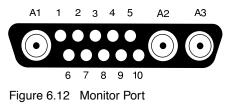

|         | 6.2.1 Monitor Port                             |      |

|         | 6.2.2 Stereo View Port                         | 6-12 |

| 6.3     | Physical Environment Specifications            | 6-13 |

| 6.4     | Microphone Specifications                      | 6-13 |

| 6.5     | Speaker Specifications                         | 6-14 |

| 6.6     | Headphone Specifications                       |      |

| 6.7     | Analog Line Level Audio Specifications         |      |

| 6.8     | PCI Module Power Specification                 |      |

| 0.0     |                                                |      |

| Section 7 | 7 Standard OCTANE Configurations   | 7-1  |

|-----------|------------------------------------|------|

| 7.1       | CPU                                |      |

| 7.2       | Memory and Storage                 |      |

| 7.3       | Graphics Configurations            | 7-3  |

|           | 7.3.1 OCTANE/SI                    |      |

|           | 7.3.2 OCTANE/SSI                   | 7-4  |

|           | 7.3.3 OCTANE/MXI                   | 7-4  |

|           | 7.3.4 Graphics Specifications:     | 7-4  |

| 7.4       | Upgrades                           |      |

| 7.5       | OCTANE Options                     | 7-5  |

|           | 7.5.1 Storage XIO Option Cards:    | 7-6  |

|           | 7.5.2 Networking XIO Option Cards: |      |

|           | 7.5.3 Video XIO Option Cards:      | 7-8  |

|           | 7.5.4 Audio Option Card            |      |

|           | 7.5.5 Other OCTANE Options         | 7-13 |

| Figure 2.1  | Attaining a 400MHz Data Rate        |     |

|-------------|-------------------------------------|-----|

| Figure 2.2  | Crossbow Connection Diagram         |     |

| Figure 2.3  | Packet-Switched Protocol            | 2-4 |

| Figure 2.4  | OCTANE System Block Diagram         | 2-7 |

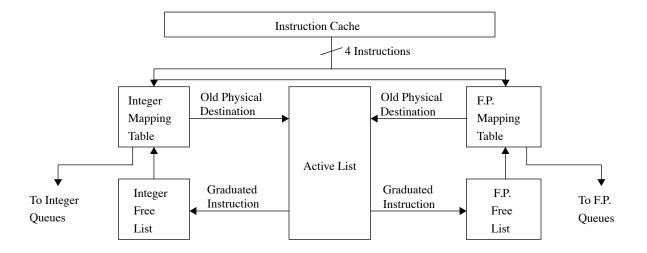

| Figure 2.5  | Instruction Mapping Scheme          |     |

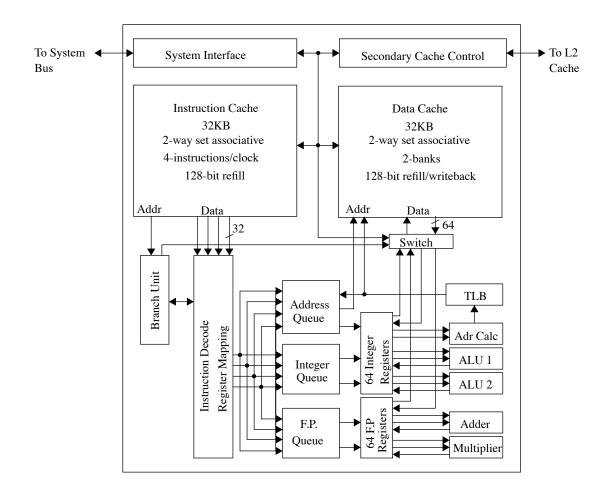

| Figure 2.6  | R10000 Processor Block Diagram      |     |

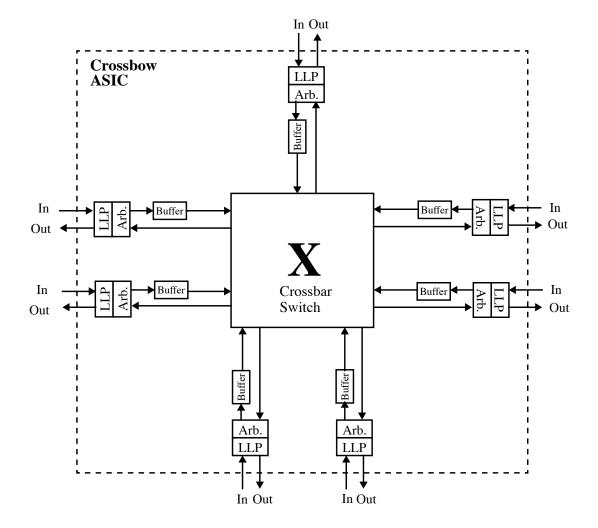

| Figure 2.7  | Crossbow ASIC Block Diagram         |     |

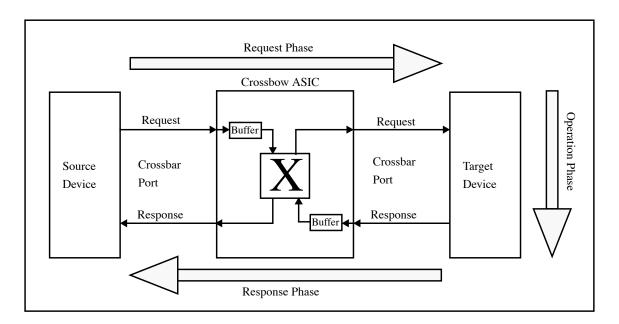

| Figure 2.8  | Packet Flow Diagram                 |     |

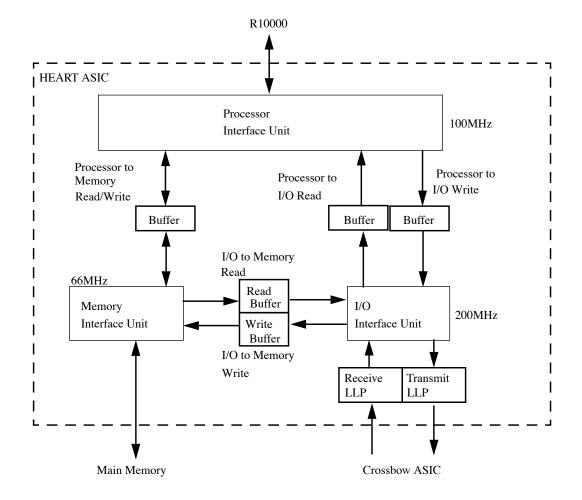

| Figure 2.9  | HEART ASIC Simplified Block Diagram |     |

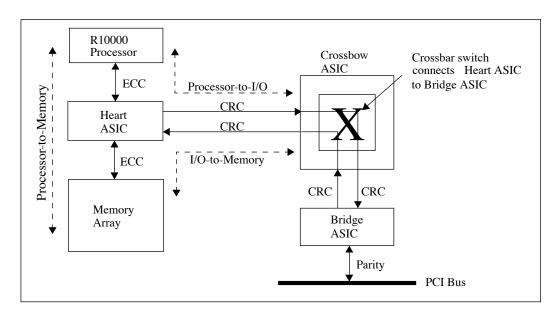

| Figure 2.10 | OCTANE Data Coherency Schemes       |     |

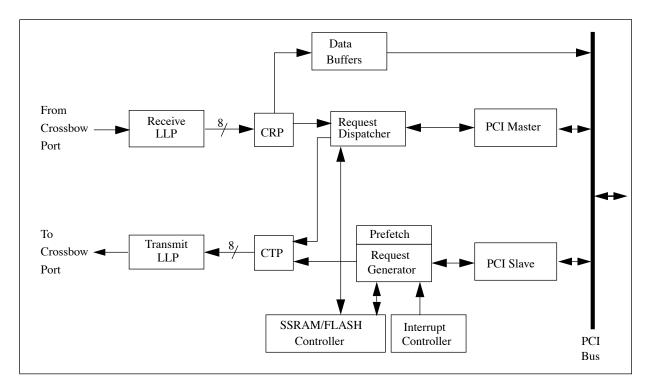

| Figure 2.11 | Bridge ASIC Block Diagram           |     |

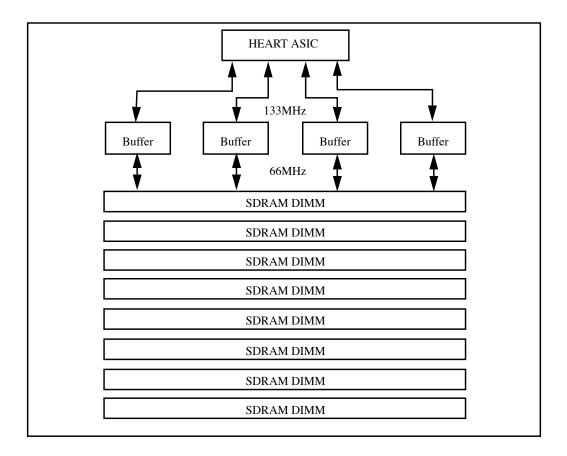

| Figure 2.12 | Main Memory Subsystem               |     |

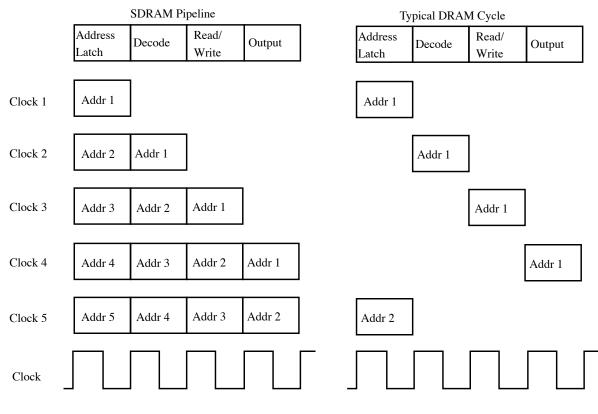

| Figure 2.13 | SDRAM Pipeline                      |     |

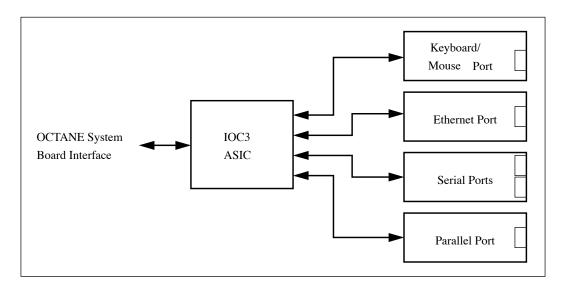

| Figure 2.14 | IOC3 ASIC Interface                 |     |

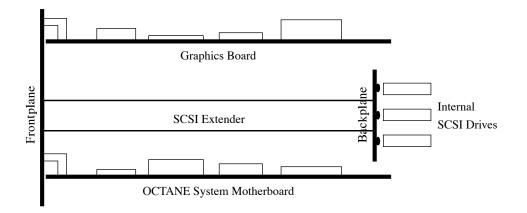

| Figure 2.15 | Internal SCSI bus Data Flow         |     |

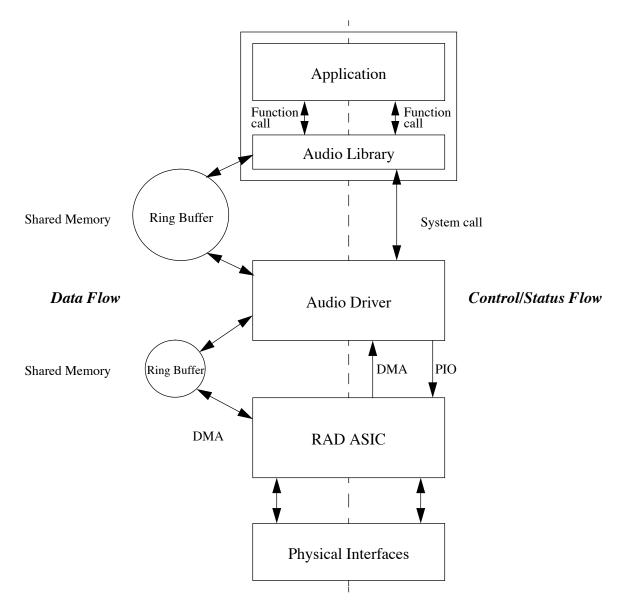

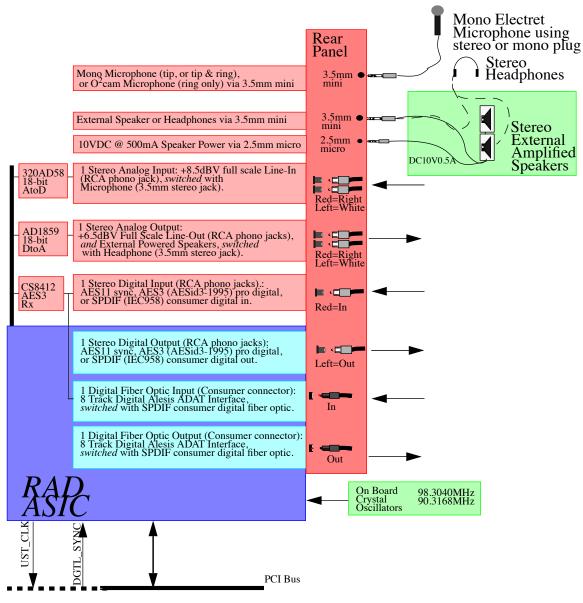

| Figure 3.1  | Audio System Flow Diagram           |     |

| Figure 3.2  | Baseline Audio System Block Diagram |     |

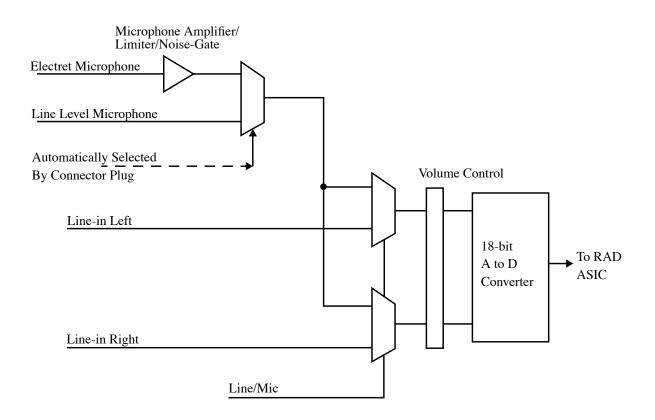

| Figure 3.3  | Baseline Audio Analog Inputs        |     |

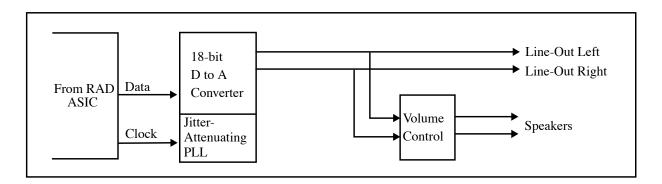

| Figure 3.4  | Baseline Audio Analog Outputs       |     |

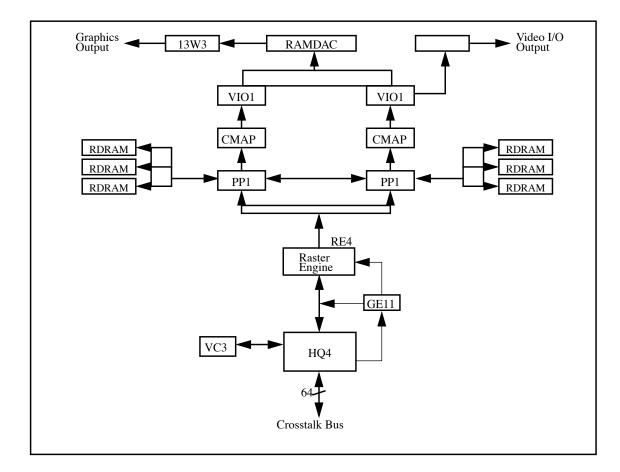

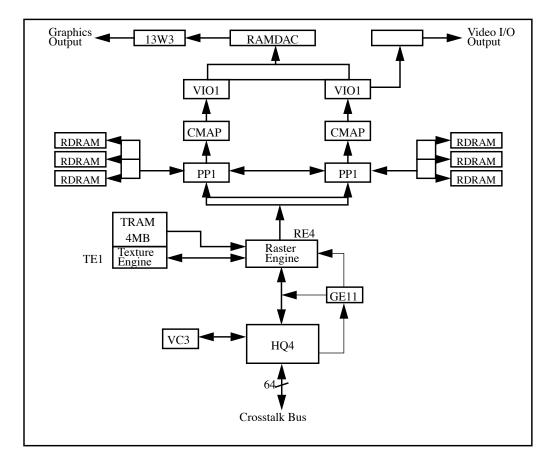

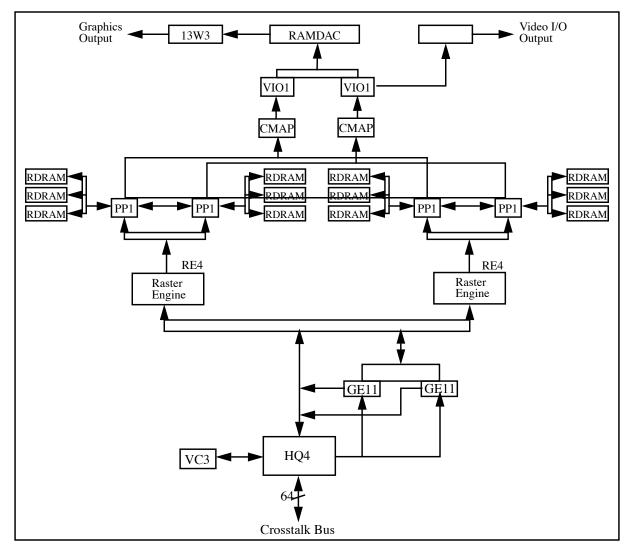

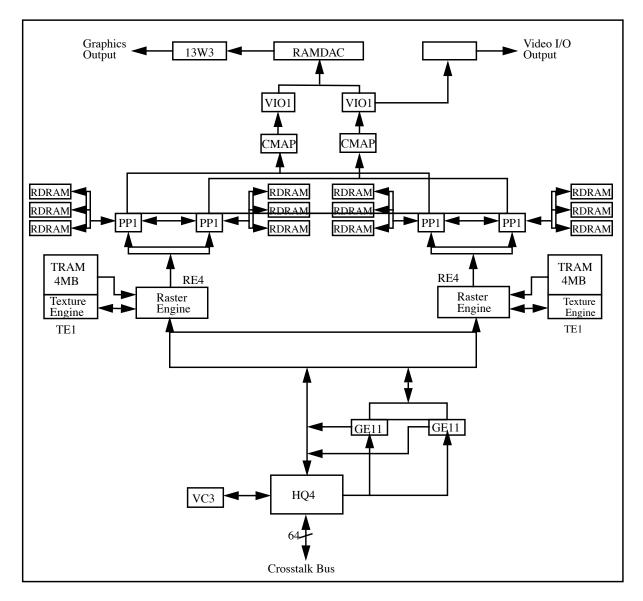

| Figure 4.1  | SI Graphics                         |     |

| Figure 4.2  | SI Graphics with Texture Option     | 4-4 |

| Figure 4.3  | SSI Graphics                        |     |

| Figure 4.4  | MXI Graphics                        | 4-6 |

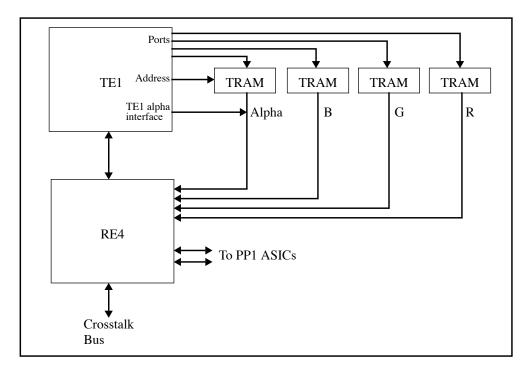

| Figure 4.5  | Texture Mapping Data Flow           | 4-9 |

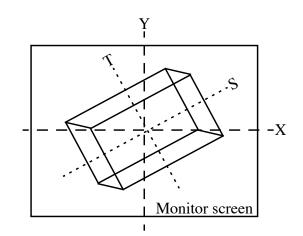

| Figure 4.6  | Spatial Coordinate Relationships    |     |

| Figure 4.7  | Graphics Subsystem Data Flow        |     |

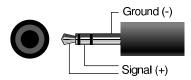

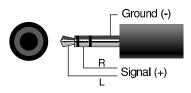

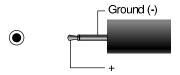

| Figure 6.1  | Microphone Port                     | 6-1 |

| Figure 6.2  | Speakerphone Port                   |     |

| Figure 6.3  | Speakerphone Power Plug             |     |

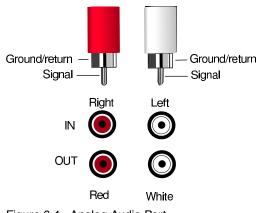

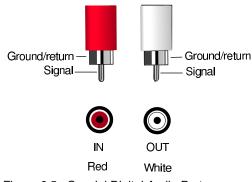

| Figure 6.4  | Analog Audio Port                   |     |

| Figure 6.5  | Coaxial Digital Audio Port          | 6-4 |

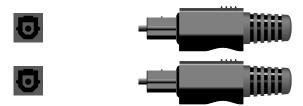

| Figure 6.6  | ADAT Optical Digital Audio Port     |     |

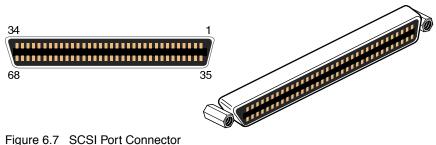

| Figure 6.7  | SCSI Port Connector                 |     |

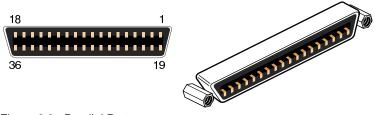

| Figure 6.8  | Ethernet Port                       |     |

| Figure 6.9  | Parallel Port                       | 6-7 |

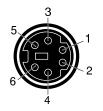

| Figure 6.10 | Keyboard and Mouse Port             |     |

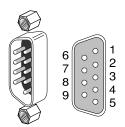

| Figure 6.11 | Serial Ports                        |     |

| Figure 6.12 | Monitor Port                        |     |

| Figure 6.13 | Stereo View Port                    |     |

List of Figures

# Section 1 Introduction

The OCTANE system delivers a new, dramatically faster, more powerful alternative for those who require state-of-the-art graphics capabilities and massive computing power in a desktop system. A radical new system architecture, focusing on data throughput, has made this significant improvement in performance possible.

The crossbar-based, symmetric multiprocessing architecture employed by the OCTANE system makes the following benefits possible:

- outstanding application performance, especially with the dual R10000 processor option

- true three-dimensional visualization

- real-time manipulation of large images

- real-time simulation involving large data sets

- simultaneous visualization and analysis of large data sets in real time

- interactive modeling and analysis of large, three-dimensional models

- high speed networking

- high, sustainable I/O bandwidth for large amounts of data

- large memory capacity (up to 2GB)

- high, sustainable memory bandwidth

An innovative approach to desktop system architecture was required to solve the system throughput limitations related to standard system architectures. While processor performance has increased over time at an exponential rate, bandwidth has not. This has created a major barrier to efficient performance, by causing lag time in both the processor and graphics systems as they wait for data to continue. Therefore, in order to improve graphics performance and take full advantage of the processor speed available today, Silicon Graphics targeted this problem. OCTANE utilizes a seven port crossbar switch to allow multiple, simultaneous data transfers rather than the one-at-a-time transfers of traditional systems. This delivers very high bandwidth and advanced bandwidth management capabilities. Each port is capable of running at 1.6GB per second peak and 1.2GB per second sustained, while the memory bandwidth is 1GB per second. OCTANE is the first true, desktop implementation of a non-blocking, multiport, crossbar in which every device has its own dedicated port; effectively improving system throughput rates and optimizing processor and graphics efficiency.

Additionally, the dual CPU option allows users to increase their processing efficiency by optimizing compute code. Applications depending on real-time data visualization and cumbersome amounts of data processing benefit especially from this type of system fine-tuning. Multiple applications can run simultaneously, while maintaining interactivity. Many applications can split processes between the processors providing an optimal compute environment for the particular needs of the user.

The enhanced version of the Silicon Graphics high performance graphical subsystem, based on the Indigo<sup>2</sup> IMPACT chip set, that is incorporated in OCTANE, provides an exceptionally high

quality of graphics at the desktop. Integrated texture mapping mechanisms and dedicated geometry hardware, combined with industry leading high fill rates and optimized OpenGL, streamline and enhance the graphics capabilities of the OCTANE system. The ability to specify the use of dual CPUs can facilitate maximum graphics performance during the simultaneous computation of non-graphics tasks.

A modular design combined with a number of options make the system highly expandable and suitable for applications with the most demanding desktop configuration requirements. The OCTANE chassis supports dual processor configurations with: four XIO slots for graphics, video, audio, and high speed I/O devices; three optional PCI-64 slots for disk; networking; and more.

The increased total bandwidth of the new system architecture, many times greater than that of Indigo<sup>2</sup> IMPACT, combined with the technical excellence of the enhanced IMPACT graphics subsystem and a high degree of expandability offer an unparalleled desktop system for computationally intensive and graphically demanding applications. The system has been designed to support a broad range of manufacturing, entertainment, defense/Simulation and scientific applications, such as:

- industrial design

- modeling

- analysis

- digital prototyping

- 3D animation

- film/video/audio

- broadcasting

- publishing

- geographic information systems (GIS)

- defense imaging

- visual simulation

- oil and gas

- chemistry

- medical imaging

A discussion of the computational needs of each of these industries, the benefits of the OCTANE system, and system configurations and options suited to each, makes up the rest of this section of the report.

# 1.1 Manufacturing

# 1.1.1 Industrial Design

OCTANE high performance graphics workstations provide industrial designers with a highly interactive and creative environment in which to realize their designs. Designers require tools that can help them create stylish, ergonomic, and effective products and communicate their product visions to others. From early ideation sketches through 3D modeling, concept evaluation, prototyping and photo-realistic renderings and animations, the digital medium continues to expand the realm of possibilities available during the industrial design process.

Two-dimensional sketching and 3D paint programs provide industrial designers with the digital equivalents of familiar tools, such as pencils, brushes and air brushes. However, in the digital environment, these tools take on far greater flexibility than is possible in the physical world. Many of these tools use texture mapping to improve visual realism.

Advanced texture mapping techniques are hardware-supported in the OCTANE system, which also has an optional 4MB of dedicated texture memory. The texture memory is a standard feature of the OCTANE/MXI configuration. The OCTANE/MXI fill rate is a desktop industry-leading 133 mega pixels per second; which is significant for tasks requiring the "painting" of large areas, such as 3D digital air brushing. Additional design functionality is made possible thanks to hardware-supported blending operations that simply draw or texture map into the frame buffer with the appropriate transparency.

The power of multiprocessing and hardware texturing made available by the OCTANE system is exploited by programs like AliaslWavefront StudioPaint 3D<sup>TM</sup> to provide features such as interactive image processing and real-time brushes. The flexibility of these tools serve not only to increase a designer's productivity, but also to spark creativity through experimentation with methods that are not possible in the physical world. The interactivity made possible by the OCTANE system is crucial to the viability of any of these tools in the work place.

Evaluating the surface quality of a detailed 3D model may involve the digital equivalent of physically holding a shiny object up to the light and viewing it from every possible angle. This would include being able to rotate it ever so slightly to detect surface flaws made visible by the way light is reflected off the surface or interference between parts. The OCTANE graphics pipeline, including hardware texturing and high bandwidth throughput, combined with programs like AliaslWavefront Studio<sup>TM</sup> delivers digital results that can provide such detailed information. Large, complex 3D models can be interactively viewed and manipulated with physically accurate lighting models and environment maps (reflections). In later stages of the design process, the multiprocessing and graphics capabilities of the OCTANE system can be employed to quickly render animations of photo-realistic images for more advanced evaluation and presentation purposes.

In many design situations, high resolution laser scans are employed to produce digital descriptions of existing physical objects. These data sets often contain over a million 3D data points. Interactive work with such data sets relies on the rapid loading, display, and manipulation of huge amounts of data. The high bandwidth data transfer capability of the OCTANE crossbar architecture is instrumental in delivering a viable environment for an industrial designer to work with such huge point clouds interactively.

Additionally, by using industrial design tools made feasible by the OCTANE system, designers can maintain the integrity of their designs by transferring accurate 3D models downstream in the design process. Multiple alternatives can be reviewed with engineers, manufacturers, and market focus groups in the same time it once took to review only a few possibilities.

OCTANE represents a new paradigm in desktop computing by facilitating early convergence of the design and analysis phases of product development. The incorporation of the advanced architecture of Silicon Graphics Origin<sup>TM</sup> servers, allows OCTANE to offer clean scalability for the entire range of manufacturing tasks from design through production.

# 1.1.2 CAD/CAM Solid Modeling

Digital modeling plays an important role in the design and prototyping phases of advanced product manufacturing processes. Applied correctly, it can dramatically reduce the cost -- in time and dollars -- required to move a product from design to production. Advanced analysis techniques coupled with the OCTANE/SSI dual processor option allow digital models to be tested and analyzed as they are being created. For instance, modelers can test digital models for problems related to strength, thermal effects, assembly conflicts, and larger scale contextual design issues as they are developing the product.

This ability to test a digital model while it is being created can significantly reduce the number of expensive and time-consuming physical prototyping cycles that must be preformed prior to actual manufacturing. Discovering form, fit, and function mistakes as they are made allows corrections to be made immediately and avoids much of the tedious process of searching for and correcting other errors that may have been directly caused by the original error.

The OCTANE/SSI is optimized for solid modeling tasks. There are three key features of the new system architecture that make OCTANE the most powerful solid modeling desktop machine available:

- the MIPS R10000 CPU

- memory bandwidth

- high speed, uninterrupted I/O

- outstanding graphics performance

Most of the leading solid modeling software packages are extremely CPU and memoryintensive. The crossbar-supported, high-bandwidth, low-latency memory of the OCTANE system, coupled with a CPU optimized for application performance, translates directly into faster model regeneration and interference checking, which facilitates more efficient design and testing operations. This in turn leads to higher quality products and a shorter product development time.

The model load times supported by OCTANE are the fastest available on any desktop system. Uninterrupted I/O is made possible by one-to-one connections between crossbar ports effectively creating a dedicated connection between disk and memory. This means that a user can for example, load a model directly from the Ultra SCSI disk to memory, without the loading operation being interrupted by other processes taking place in the system such as the arrival of data over a network connection.

Silicon Graphics has always been known for its powerful graphics accelerators. The OCTANE system provides additional strength to this reputation in the display of large scale, complex 3D solid models. Often the limiting factor in this task is the transformation of three-dimensional model data into the two dimensional data required for display. The OCTANE system employs a hardware Geometry Engine® (960 MFLOPS RDRAM) to perform the transformation of vast amounts of three-dimensional information found in large digital models into an image that appears on the monitor. This hardware geometry engine acts like a powerful co-processor that relieves the CPU of repetitive geometry calculations. Its design avoids some of the trade-offs that are necessarily a part of a general purpose CPU, making it even more efficient than the CPU for geometry computation. One unique feature of the hardware Geometry Engine ASICS of the OCTANE system is that, unlike CPU-based geometry systems, it can be scaled. Adding a second chip yields twice the performance.

Because the OCTANE graphics subsystem is able to process 3D models so quickly, it is important to be able to provide it with data at an equally high rate. The new system architecture supplies the high bandwidth needed to keep the graphics pipeline full. The result is fluid interaction even with very complex assemblies.

The OCTANE/SSI is the ideal desktop machine for demanding professional modeling applications. It incorporates two Geometry Engines, delivering enough power to allow component designers to manipulate and view entire assemblies, test components, and analyze interactions within assemblies all with the same desktop machine.

# 1.1.3 Analysis

OCTANE provides unprecedented power in a desktop system for engineering analysis applications in which the computational demand for rapid processing of huge data sets -- terabytes in some cases -- is crucial. OCTANE is the first desktop computer that can effectively support both design and analysis simultaneously. With OCTANE, it is no longer necessary to ship large simulation jobs off to a mainframe for computation. Design, analysis, simulation, optimization, and visualization can all take place at the same desktop station.

Engineering analysis software is computationally intensive, requiring strong floating-point performance, symmetric multiprocessing, high-speed memory and I/O systems, and 64-bit processing. Leading engineering analysis solutions have historically taken advantage of these capabilities on Silicon Graphics systems with the powerful scalability of the POWER CHALLENGE<sup>TM</sup> and Origin supercomputers. With the advent of the OCTANE system, many of these advanced capabilities are now available on the desktop.

The dual processor option, coupled with the high performance graphics and I/O subsystems, make OCTANE extremely flexible and an exceptionally productive tool for manufacturing analysis. With OCTANE:

- both CPUs may be applied to an analysis problem, with the graphics subsystem being used for visual analysis; or

- one CPU can be dedicated to analysis, while the other provides the processing power to work interactively with a design model

Most leading solid modeling applications support a seamless integration with advanced engineering analysis packages, facilitating both paradigms. The new non-blocking, multiport,

crossbar-based system architecture eliminates the lag time inherent to the single-path-for-alldata design of traditional shared bus architectures. This results in exceptionally high bandwidth to and from disk and graphics bandwidth, facilitating simultaneous analysis and interactive modeling for the first time on a desktop system.

OCTANE is the first system to provide high performance compute power capable of facilitating the analysis of huge data sets and the visualization of results all in a compact, widely deployable desktop computer.

# 1.1.4 Digital Prototyping

Digital prototyping is an emerging technology pioneered by some of the leaders in the automotive and aircraft industries to optimize designs and reduce costs. With the growing power of desktop computing systems, this technology is moving into more and more areas of manufacturing. Digital prototyping allows engineers to review assemblies and subassemblies, as well as monitor part movements and digitally check for interferences without having to build an actual physical prototype.

Digital prototyping requires the fastest graphics available for real-time interaction with large models. OCTANE provides the most powerful desktop visualization machine available; this allows engineers to verify full assemblies before the first metal is cut.

In dual processor systems, an application that takes advantage of dual CPUs will naturally perform better. For example, an optimized digital prototyping application might assign one CPU to culling objects (removing objects from the scene that cannot be seen), and the other to sending drawing commands to be rendered by the graphics system. 4D Navigator by CATIA/ CADAM<sup>®</sup> is an example of a digital prototyping application that uses this technique, resulting in a significant improvement in running performance.

Most of the leading solid modeling applications provide seamless integration with advanced engineering analysis packages. The high memory bandwidth of the crossbar-based system architecture, coupled with the floating-point performance and 64-bit processing of a MIPS R10000 CPU, support the high level of compute and graphics power needed to run both the three-dimensional solid modeling and the analysis aspects of digital prototyping applications. Dual processors allow complex analyses to take place in the background while an engineer continues to work interactively on the model, dramatically shortening the critical design/test cycle of the product development phase. One processor may even be used as an Intranet server for the revision control system used by a team working on a single assembly, without adversely affecting an engineer's design work on the same machine.

OCTANE supports in-context design of medium to large sized assemblies and subassemblies, such as those involved in designing products in the automotive industry. Components can be quickly reviewed as part of larger assemblies without having to wait for costly physical prototypes. The OCTANE system user is not burdened by the tediously long processing times associated with conventional systems that tie up the CPU. Virtual reality techniques can also be used to identify and resolve design and manufacturing problems early on.

The OCTANE/SSI configuration with dual processors provides the ideal desktop system for digital prototyping applications. Reduced analysis/design iteration time, real-time interaction with models and assemblies, and graphics speed are optimally supported by the symmetric

multiprocessing capabilities and high system bandwidth of the OCTANE system architecture. This translates directly to lower development expenses, shorter development time frames and higher quality products.

# **1.2 Entertainment**

# 1.2.1 3D Animation

Computers have become indispensable tools in a number of entertainment related fields, including:

- special effects and post production applications for both film and video

- · nonlinear editing, such as that required for creating commercials and editing video

- broadcasting, which can involve weather graphics and other on-air graphics

- game content production

The OCTANE system's revolutionary new system architecture defines the direction for the next generation of desktop visualization workstations. It enables the R10000 processor, also present in the Indigo<sup>2</sup> and O2 systems, to perform as much as 70% more efficiently. The high bandwidth, low-latency system allows users to perform tasks never before achievable on desktop computers. Trends in the entertainment industry reflect a growing demand for capabilities such as uncompressed, nonlinear editing and animation of extremely complex, 3D sequences. The OCTANE architecture offers a vehicle for delivering outstanding capabilities to creative professionals in the entertainment industry.

An OCTANE equipped with the high-powered OCTANE/MXI graphics system, dual R10000 processors, OCTANE Digital Video and Compression, and high-speed networking is an ideal workstation for any 3D animator. This collection of technology is powering the next generation of software applications from a number of leading animation developers. It is well suited to complex animation tasks, such as: full scene animations and modeling, or the animation of intricate, organic characters. Dual processors allow animators to simultaneously work with wireframe models and view photo-realistic final rendered images previewed in real time. This is achieved by using one CPU for interactive animation, while the other CPU is occupied with re-rendering the parts of the final image that are changed by the animator. This streamlines the production process and eliminates the waiting time previously associated with test rendering.

The OCTANE Compression card allows animators to play back a motion test sequence at full resolution on an interlaced composite or S-Video monitor without adding an external RAID or DDR. Motion tests can also be played back at full video resolution on the graphics monitor, previewed at video frame rates, or played back in loop mode for synchronization purposes, all without compromising the system performance. This ability to quickly render a set of test images, using the same desktop machine that is used for production, is an extremely valuable and time-saving asset for any production team.

Compressed or full-resolution uncompressed video can also be texture mapped in real time and inserted into a scene to provide rich detail without requiring extensive modeling or animation. Items such as blinking control panels, video billboards, and background settings can now be included as video segments textured onto polygons - all rendered in real time.

Post production processing typically involves combining live footage, audio data, and computer-generated animation and special effects. OCTANE is the first desktop workstation capable of achieving the necessary processing power to support this kind of data-intensive work. Thanks to high speed interconnects between ports provided by its crossbar-based

architecture, OCTANE is able to move an unprecedented quantity of data around the system at speeds previously unattainable in a desktop system.

Game developers can also profit from the graphics and processing performance made possible by the OCTANE system architecture. New games can now be prototyped and played with fully textured, real-time 3D characters. This allows developers to thoroughly evaluate a game concept prior to having the game code written. Once a new concept has been approved, 3D models can best be created and animated using any of the industry-leading software tools that take full advantage of the OCTANE system's unique and powerful computing and graphics capabilities.

OCTANE can increase an animator's productivity dramatically. The ability to test render sequences in real or near real time also allows animators the creative freedom to test a wider range of options without compromising on other aspects of production. The interactive performance of OCTANE coupled with the ability to preview sequences in a form approaching final rendered quality and frame rate helps eliminate guess work. Additionally, support for simple, on-the-fly compositing between live video and computer-generated animation make OCTANE a natural choice not just for high end entertainment applications, but also for fast turn around industries such as news broadcasting.

# 1.2.2 Film/Video/Audio

Real-time, nonlinear, uncompressed, multistream, online editing is now possible at the desktop level thanks to the radically new OCTANE system architecture. The seven port crossbar-based system replaces the one-after-the-other processing bottleneck of traditional system architectures, with symmetric multiprocessing. In combination with a memory bandwidth designed to keep the R10000 processors running flat out, this makes OCTANE the first desktop system capable of supporting uncompressed, multistream editing.

The function of the crossbar switch is similar to that of a video router. It allows data to flow inside the system without interruption. The crossbar contains bandwidth management hardware that can dedicate system resources to ensure that audio and video streams are processed in real time. The high bandwidth of the crossbar (1.6G per second per port peak and 1.2GB per second per port sustained) can handle many simultaneous streams of uncompressed video.

OCTANE provides two channels of 10-bit CCIR-601 video in and out, as well as disk interfaces (such as Ultra SCSI and Fibre Channel) fast enough to store two streams to disk in real time. The base system comes equipped with two Ultra SCSI buses, and three internal 3.5" drive bays that can store up to 27GB of data. Additional Ultra SCSI or Fibre Channel interfaces can be added through PCI or the high-speed XIO bus. Video processing is supported by the OCTANE graphics subsystem.

The OCTANE Digital Video option provides dual input and dual output channels of SMPTE 259M digital video, CCIR serial digital video. The video can be PAL or NTSC timing and 8- or 10-bits per component. The two 4:2:2 inputs can be used together for dual linked signal with video and key. It also supports genlocking and has a blender/keyer which supports chroma and luma keying and blending of live CGI with video. Additionally, a high quality YUV/RGB colorspace converter and video texture port are standard features of the board. This allows real-time, high quality colorspace conversion and the use of live video as a texture map on any 3D

geometry. This translates to true, high quality, 3D digital video effects, unlike those produced by most black box solutions, which rely on inferior 2D, coefficient-based transformation tricks.

For film applications, OCTANE supports real-time manipulation on 1Kx512 streams and realtime display of 2Kx1K - high density television resolution. The OCTANE Compression option is also available for those applications that deal with films requiring greater resolution. It supports one or two real-time video streams at up to 2:1 JPEG compression.

OCTANE provides hardware-supported synchronization between audio and video streams. The baseline audio capabilities of the OCTANE workstation are a generation ahead of the competition. The powerful audio capabilities of OCTANE include 18-bit analog stereo I/O, 24-bit AES I/O (stereo) and 24-bit ADAT Optical I/O (8 channels). The sample rates are adjustable and can be locked to external time bases or to the internal video timing reference bus.

The OCTANE family of workstations support professional video, film, and audio work to a degree never before possible with a desktop computer. Uncompressed nonlinear editing, film resolution effects and real-time interaction with complex 3D scenes are just some of the many solutions powered by the technical innovations of the OCTANE system.

# 1.2.3 Publishing

The advantages of digital media in terms of speed, functionality and flexibility for publishing, prepress and related disciplines are well known. The new OCTANE system architecture offers industry-leading advances in key areas of system functionality relevant to these applications. Data handling speed, supported by true multiprocessing capabilities; superior, hardware-based image processing; and hardware-supported texture mapping are just some of the important features that OCTANE offers.

Because the size of graphic data can be very large -- 300 to 600 dpi for simple pixel images can quickly add up to gigabytes worth of data -- the ability to transfer data quickly and efficiently around the system becomes crucial to interactive work and rapid display update. The bottleneck commonly associated with this data transfer has been eliminated by the new crossbar-based architecture of the OCTANE system.

The OCTANE crossbar, in which every device has its own dedicated port, is the first truly nonblocking, multiport, crossbar implementation in a desktop system. It supports direct, simultaneous, port-to-port data streams of 1.6GB per second peak and 1.2GB per second sustained. These high speed data paths form disk-to-memory and memory-to-graphics subsystem, allowing processors and the graphics board to run more efficiently.

Fast image processing capabilities are a prerequisite for any system supporting advanced imaging, enhancement, and filtering features, such as: color correction, painting, retouching, drawing, and image compositing. Most image processing operations done on the OCTANE system are hardware-accelerated through the OpenGL API. The optimized interface of OpenGL on Silicon Graphics systems insures maximum possible graphics and imaging performance. The highly effective OCTANE system architecture and OpenGL interface provide unprecedented image processing capabilities in a desktop machine.

Two-dimensional texture mapping supports interactive image manipulations, such as rotation and zooming. It is also the most efficient method of implementing paint brushing with large air brushes, because the fastest method to display pixels on the screen is to texture map them from texture memory on to the frame buffer. The associated fill rate on an OCTANE/MXI is about 133 Mega Pixels per second; improved from approximately 119 Mega Pixels per second on an Indigo<sup>2</sup> Maximum Impact. Barco Graphics, DALiM Imaging, Contex, and Heidelberg Prepress depend on the power of hardware texture mapping to satisfy their prepress needs.

Color conversion is specifically supported in two portions of the image processing pipeline of the Impact graphics subsystem. Linear color space conversions can be accomplished by means of a color matrix, while nonlinear color space conversions can be performed via a three- or four-dimensional lookup table and the texture subsystem.

Multiprocessing and expandability are two important features of the OCTANE system. The dual processor option allows one CPU to be assigned the task of reading data off the disk, while the other is occupied with feeding the graphics subsystem. One CPU might also be used to handle batch processes, such as lamination, auto trapping or prepress color separation, while interactive editing independently utilizes the second CPU. Multiple PCI slots make connecting hot swappable RAIDs and third party boards for scanners, image setters, and other external devices very convenient.

OCTANE/MXI and OCTANE/SI with texture, both with the dual processor option, are ideal desktop stations for publishing, prepress, and related disciplines that deal with text, image and graphic data. High speed data transfer capabilities combined with the industry-leading OpenGL programmable Impact Graphics subsystem, advanced multiprocessing capabilities and a high degree of expandability make OCTANE an excellent choice in desktop systems for this industry.

# 1.3 Defense/SImulation

# 1.3.1 Defense Imaging

OCTANE provides a desktop alternative for defense applications that typically require the best possible balance between processor speed and data resolution. The new crossbar-based architecture supports high speed, multiprocessing that dramatically improves the efficiency of the overall system by effectively removing the one-at-a-time, data transfer bottleneck built into conventional desktop systems. This results in the kind of computation and graphic speed necessary to power complex analysis, simulation, and training applications. It is the ideal desktop station for a wide array of tasks, including:

- situational assessment

- mission planning

- intelligence analysis

- previewing

- simulation

- rehearsal

- space operations

- satellite tracking

- animated satellite weather imagery

The OCTANE system allows aerospace and defense customers to create large, detailed models interactively with virtual prototyping and virtual manufacturing applications. Software, such as ENVISION and IGRIP<sup>®</sup> by Deneb Robotics, provide much greater fidelity in physics-based engineering models by taking advantage of the unique features of the OCTANE system architecture. The kinematic and dynamic properties of the mechanisms support real-time reactions to immersed participant input.

The new, crossbar-based architecture of the OCTANE system facilitates unprecedented data transfer rates for a desktop machine by replacing conventional transfer mechanisms with the first truly non-blocking, symmetric multiprocessing, multiport crossbar in a desktop system. The resulting high system bandwidth (1.6GB per second per port peak and 1.2GB per second per port sustained) provides substantial improvements in performance for a wide array of applications.

Advanced, hardware-supported texture mapping techniques, combined with the industryleading graphics subsystem and an optimized OpenGL interface, allow the huge amounts of data supplied by satellites and other sources to be combined with three-dimensional models and other information at speeds never before possible with a desktop machine. Dual processors allow one processor to be dedicated to feeding the graphics subsystem, while the other takes care of analysis computations and other tasks. This means a higher guaranteed frame rate for the often oversized data sets involved in defense applications; an asset of particular importance for simulation and training applications.

Many of the OCTANE XIO options can make the system even more attractive for defense industry applications. 4-port Ultra SCSI channels allow a large array of additional disk drives to be added to the system for the massive amounts of data that typically have to be accessed by

defense applications. An alternative to SCSI for external disk arrays is the much faster, fiber optics-based Fibre Channel. Presenter, a flat screen 16-bit, 1280x1024, high resolution screen, makes the OCTANE deployable even at difficult sites - for instance, a remote navy base, or the back of a truck.

The availability of massive computing power, huge system bandwidth, and industry-leading graphics, all in an affordable desktop model, make OCTANE an attractive choice for the wide variety of highly data-intensive tasks that define most defense applications. OCTANE/MXI with integrated texture memory or OCTANE/SI with the 4MB of optional texture memory are the best configurations for meeting defense industry needs.

# 1.3.2 Visual Simulation

The OCTANE system provides the compute power and bandwidth required for data-intensive simulation tasks. Real-time, deterministic simulation is key to any successful simulation application where quality equates to the ability to maintain the best possible picture at a prespecified framework. For an operator-in-the-loop simulation, this means a guaranteed frame update rate of 30Hz or greater, in order to avoid distracting visual anomalies. Training and engineering analysis simulators depend on this to closely simulate real life situations and conditions. Typical visual simulation applications include: flight and driving simulators; aircraft part task training; ship bridge training; and engineering analysis simulators that evaluate such things as pilot work load or performance.

Sophisticated texture mapping techniques combined with a high fill rate reduce dependence on extremely complex geometric models, although it is still important to maintain good geometry performance. OCTANE incorporates the industry-leading desktop geometry and fill rates introduced in the Indigo<sup>2</sup> IMPACT, with streamlined texture mapping performance via 4MB of dedicated, high-speed texture memory. This significantly increases the speed at which individual frames can be generated. The new crossbow-based architecture increases system bandwidth, which enables considerably faster memory access for those scenes that require larger texture data bases. This translates into a higher quality image at a set, guaranteed frame rate.

The multiple processor configuration of OCTANE allows one processor to be assigned exclusively to rendering tasks, while the other handles all non-graphic tasks including analysis. Typically operator input is fed to the kinematics (or motion) model for conversion, processed based on a physical model, and the results -- a new position and attitude -- are generated. This is done for both human operator controlled and computer operated vehicles and objects. The dual processor configuration allows these calculations to be done without interfering with the actual rendering process.

Taking advantage of the REACT<sup>TM</sup> real time extensions can also provide non-degrading processing priorities, improved system latencies and processor/memory locking, all of which add up to a system that is able to deliver superior, consistent, real-time behavior for simulation tasks.

The dual head option typically allows the texture equipped head to process texture, while the other takes care of user interface controls. Both heads support 24-bit color and hardware-accelerated geometry. The multiple channel option can also be used to route results to more than one screen to simulate wrap-around views of a scene.

OCTANE systems will be used in a number of different capacities, such as modeling stations to build scenes required for simulations; image generators for scene simulation in both single and multiple-window views; instructor and operator control stations; and compute stations for physics-based dynamic models.

# 1.3.3 Geographic Information Systems (GIS)

OCTANE is the first desktop system ideally suited to support GIS professionals as they link, analyze, and manipulate massive data sets containing geographically referenced resource data. GIS software must facilitate interaction with numerous types of geographically related data, including topographic, demographic, utility, facility, image and other types of data that are commonly part of a GIS data set. The data must also be displayed at an appropriately fast rate to support interactive work. Typically, more than one of these types of data -- terrain, maps, roads, buildings, symbolic markers, etc. -- must be displayed simultaneously. Dual processor OCTANE/SI with texture and OCTANE/MXI provide optimized hardware support for software that delivers such functionality.

The two most crucial aspects of a GIS system are fast data paths and fast graphics. OCTANE delivers both at a level never before supported in a desktop system. The crossbar-based IO architecture avoids data transfer bottlenecks associated with conventional desktop systems by furnishing remarkably high bandwidth between the various subsystems. This allows data delivery at an unprecedented rate and dependability.

Fast graphics, including advanced hardware-supported texture mapping techniques, allow huge data sets to be interactively manipulated two- and three-dimensionally. On OCTANE, most image processing operations are hardware-accelerated through the OpenGL API. This allows programmers to easily take maximum advantage of graphics and image performance potentials, smoothing three-dimensional data roaming and improving the overall graphics capability of the system.

Multiple layers of both two- and three-dimensional data are sent from disk to memory and from memory to the graphics subsystem; where hardware image processing occurs. Operations that enhance raster data, such as Landsat or aerial images, are extremely data-intensive. Sharpening, edge detection, and complex feature extraction, like finding a corn field based on multispectral data, require the IO bandwidth and graphics power that OCTANE provides.

The dual processor option allows one processor to deal with transferring data from the disk, while the other is dedicated to feeding the graphics subsystem for processing and display. Multiprocessing also improves batch processing of multispectral data that is not displayed. For extremely demanding data delivery, the multiport Ultra SCSI option provides fast access to data at over 80MB per second.

For serious GIS applications involving multiple layers of data that require two- and threedimensional interactivity and rapid frame updates, the OCTANE system provides an exceptional desktop option. Dual processor OCTANE/SI (with the 4MB texture option) and OCTANE/MXI (with built in dedicated texture memory) both offer the data access and graphics power required for handling the complex and oversized data sets typical of GIS projects.

# 1.4 Sciences

# 1.4.1 Oil and Gas

The OCTANE system is ideal for exploration and production tasks related to the energy industry. It allows extremely data and compute intensive geological applications involving huge geologic databases, reservoir characterization tasks, mapping and modeling to be dealt with on the desktop. Other energy related applications, such as seismic acquisition, seismic processing, and seismic interpretation, as well as reservoir engineering, statistical analysis, refinery and platform design, engineering analysis, and process simulation also benefit from the OCTANE system's generous memory bandwidth and high speed, uninterrupted I/O.

The characteristically large data sets of 1GB and more that are required for most oil and gas related visualization and analysis tasks are handled with revolutionary ease by the OCTANE desktop system. Its new crossbar-based architecture supports multiple data streams, thus avoiding the lag time caused by conventional desktop routing systems. Large data sets can be accommodated by three 3.5" drive bays of internal disk storage, which can provide a combined total of 27GB of disk space. The dual CPU configuration option available with OCTANE, combined with the crossbar system architecture, guarantees substantially higher performance efficiency and speed.

Particularly data- and processor-intensive tasks such as data roaming can be handled at a remarkably faster pace, thanks to more efficient data and bandwidth management made possible by the crossbar. Symmetric Multiprocessing, facilitated by the crossbar, allows data to flow from disk to memory and from memory to graphics without degrading lag time; both processes are able to run at full speed without interfering with each other. Volume roaming, used to magnify interactively selected portions to a data set being visualized, can operate at rates up to 50 times faster than that which is possible on a system based on traditional desktop architecture.

The OCTANE system provides the memory bandwidth required to keep the R10000 processor(s) running flat out, boosting overall application performance and data handling capacity. This combined with its industry-leading graphics system make it an ideal system for data-intensive oil and gas applications, including volume rendering and roaming.

# 1.4.2 Chemistry

OCTANE workstations are powerful and productive interactive desktop systems for chemical and pharmaceutical customers. OCTANE combines outstanding three-dimensional visualization with high-end number crunching capabilities. The enormous compute demands of molecular modeling and process simulation -- together with the extraordinary information management requirements of chemical database mining, structure elucidation, and bioinformatics -- greatly exceed the capacity of conventional desktop computers. The radically new system architecture employed in OCTANE changes that by replacing the one-at-a-time data transfer mechanism of common desktop systems with a multiport crossbar. This effectively allows the processors and graphics subsystem to work flat out; dramatically improving overall system performance.

For customers studying proteins, polymers and other large molecules using molecular modeling, molecular visualization, X-Ray and NMR Structure Determination and using advanced quantum chemistry and other computational chemistry and bioinformatics methods, OCTANE workstations are an ideal balance between computing capabilities and the highest level of three-dimensional graphics. OCTANE workstations offer:

- the availability of over 800 chemistry and biology specific applications, including parallelized applications

- outstanding application performance with dual R10000 processors

- true three-dimensional visualization

- fast networking

- large I/O capability

- high, sustainable I/O bandwidth

- large memory capacity (up to 2GB)

- high, sustainable memory bandwidth

- the availability of the full range of SGI collaborative and desktop tools

The dual processor option facilitates the ability to interactively run graphics from one CPU while running compute jobs on the other. The R10000 processor provides outstanding uni- or multiprocessor performance for molecular dynamics or mechanics applications, homology modeling, or the study of electronic structures using quantum methods.

The OCTANE system's industry-leading graphics subsystem and hardware-supported texture mapping solve a wide range of visualization needs, including Stereo-in-a-Window and high resolution stereo viewing. Like all Silicon Graphics products, OpenGL runs optimally on the OCTANE system, allowing programmers to easily take advantage of a number of unique Impact graphics features and control the performance of the graphics portion of their applications.

OCTANE is also attractive as a client and server system for customers needing to access and serve chemical compound and structural databases such as: ISIS/Host by MDL; Unity by Tripos; RS3 by Oxford Molecular; C2 Catalyst by MSI; ChemX/Diversity by Chemical Design; or Thor and Merlin by Daylight CIS. Thanks to the high system bandwidth provided by the crossbar-based architecture, OCTANE is able to provide:

- fast local processing power for creating, submitting and analyzing queries

- fast local processing power for serving departmental databases

- parallelized two-dimensional, three-dimensional and reaction searching in applications like ISIS/Host and Unity

- outstanding network connectivity

- up to 2GB of memory for in-core searching, such as those performed by Daylight CIS applications

- and outstanding data mining and data visualization functionality

For computational biologists manipulating and analyzing sequences of DNA and performing "structure prediction" using techniques like homology modeling and protein or crystal structure prediction, OCTANE offers a number of advantages. It provides: outstanding local

CPU performance and scalable parallel performance on a wide range of bioinformatics applications like FASTA, BLAST, Smith Waterman and other homology search tools; fast network access to intranet and Internet application servers; biological desktop and integration software; leading genetic database systems for managing high-throughput bioinformatics environments; complete use of the SGI Cosmo web execution and development environments.

OCTANE is the ideal desktop workstation for chemistry research, teaching, and application tasks. The well-balanced high speed computational power and industry-leading threedimensional graphics facilitated by the new crossbar-based, high bandwidth system architecture are without compare. Symmetric multiprocessing makes typically oversized data sets accessible at rates never before seen in a desktop workstation. OCTANE streamlines the way things are done by making simultaneous analysis and real-time visualization of results possible.

# 1.4.3 Medical Imaging

Many sophisticated data acquisition devices are now available for gathering critical information for clinical diagnostic and medical treatment planning purposes. Image precision and speed are both crucial aspects of medical imaging. Time spent acquiring data from individual patients is very expensive. This, combined with the need for highly accurate images, means that data acquisition has to happen at the highest possible speed and volume. As the resolution of diagnostic images increases and the time available for acquisition shrinks, systems that collect, process, and display the data must be able to provide sufficient and reliably consistent computational power and data processing speed.

OCTANE supports standard industry data acquisition and manipulation procedures exceptionally well. It performs routine procedures efficiently, such as processing data collected by a medical data acquisition device in order to quickly supply alternate two- and threedimensional views of an entire data set. Arbitrarily oriented slices of acquired medical data sets are generated interactively and viewed from any angle. Another core functionality fully supported by OCTANE is interactive windowing. Subtle changes in data can be differentiated via simple, interactive adjustment to the lookup table.

OCTANE is also the industry-leading desktop system for emerging, sophisticated, 3D visualization techniques. It supports interactive surface and volume rendering, which facilitate interactive visualization of volumetric representations of data sets. Although these techniques will not replace the diagnostic value of cross-sectional images in most cases, they will become invaluable tools in cases involving complex topologies, such as tracking vessels involved in aneurysms; tracking gyral convolutions in neurosurgical cases; and preparing and performing maxillofacial surgical applications. These techniques can greatly enhance the diagnostic process and treatment effectiveness in such cases.

NMR, MRI, CT, US, PET, and SPECT are just a few of the systems that will benefit from the OCTANE system's unique data processing features. The dual CPU option and high bandwidth design provide the necessary power and speed to support high-end medical imaging needs. The OCTANE system can be used during the data acquisition and reconstruction phase as a console for diagnostic scanners. Dedicated CPU, priority I/O and guaranteed bandwidth make it a highly reliable solution for use in the acquisition phase. The OCTANE system's superior graphics capabilities also make it an ideal vehicle for two- and three-dimensional visualization,

interactive viewing, and manipulation of acquired medical data for diagnostic and treatment purposes.

# Section 2 System Architecture

#### 2.1 Architectural Overview

The design of the OCTANE system sought to address issues such as bus bandwidth, true support for real-time digital video and audio streams, and system modularity. In order to solve the bus bandwidth limitations common in shared-bus architectures, it became necessary to design a system which did not adhere to the shared-bus paradigm. In addition, the new system architecture had to accommodate the large bandwidth required to support these real-time data streams. The idea of system modularity became necessary in order to support future generations of processors, memory, and I/O devices with a minimal amount of re-design. The following sections discuss some of the design principles and techniques used in the OCTANE system.

# 2.1.1 Bus Bandwidth and Frequency

The majority of bus architectures on the market today are known as shared-bus architectures. Some of the more common include PCI, EISA, and AT. In a shared-bus architecture, all of the peripheral devices connect to the bus through one set of wires which are routed across all of the connectors. These wires are in turn shared by all of the peripheral devices.

Bus bandwidth is defined as the number of bits which can be transferred between the peripheral and the system during a given time period, usually noted in Megabytes per second (MB per second). Bus bandwidth is determined by two variables; the number of bits supported, and the frequency at which the bus operates (bits x frequency). There are two common techniques for increasing bus bandwidth in a shared-bus system: increasing frequency, and increasing the number of bits or width of the bus.

All peripheral devices in the system must share this bandwidth. While increasing frequency can offer some initial performance improvement, having multiple distributed loads along a single set of wires limits the maximum frequency at which these wires can be driven. In a shared bus architecture, frequencies above approximately 50MHz become impractical as signal integrity is greatly diminished.

Another common technique is to increase the size of the bus. Common bus sizes are 8-, 16-, 32- and 64-bits. Going to 128-bits is somewhat impractical because the device becomes dominated by the physical bus connections required to facilitate these wide data paths. This in turn requires larger more expensive packages to support these large bus sizes.

# 2.1.1.1 The Crossbow Solution

The Silicon Graphics OCTANE system uses a mechanism called a crossbar switch, incorporated into the *Crossbow* ASIC, to provide solutions for both the frequency and bandwidth problems.

# **OCTANE** System Architecture

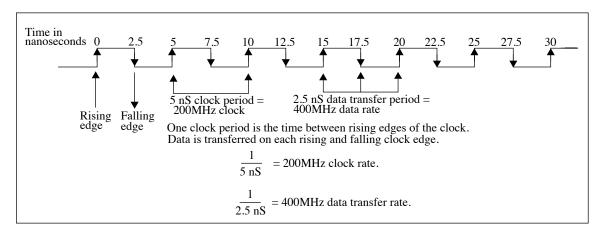

The OCTANE system addresses the signal integrity problems which arise at higher frequencies by using dedicated connections between the peripherals and the Crossbow ASIC. This solution allows two devices to talk to one another over a pair of 16-bit unidirectional point-to-point links running at an effective 400MHz data rate using both edges of a 200MHz clock. In most computer systems information is transferred only on the rising edge of the clock. In an environment operating at 200MHz, a rising clock edge occurs every 5 nanoseconds (nS). This is called the clock period. The Crossbow ASIC not only transfers data on each rising edge of the clock, but also transfers data on each falling edge of the clock. This means that data is transferred every 2.5 nS, which equates to a 400MHz data transfer rate. Figure 2.1 shows how data is transferred relative to the 200MHz clock.

Figure 2.1 Attaining a 400MHz Data Rate

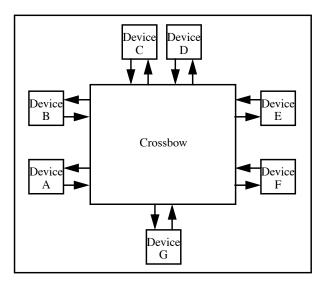

These unidirectional wires on each Crossbow ASIC device interface are not shared with any other devices in the system. This allows for a controlled electrical environment where the impedance of the traces is known and does not fluctuate. There is one driver and one receiver. Having dedicated connections allows for the preservation of signal integrity via tight control of transmission line effects and the minimization of clock skew. The mechanism used for these dedicated connections is called 'low-voltage-swing signalling' or STL (SGI Transistor Logic). Figure 2.2 shows a simple Crossbow connection diagram. The various devices represent those components in the system which interface to the Crossbow ASIC. These include the Heart ASIC, two Bridge ASICs, as well as graphics and expansion cards.

Figure 2.2 Crossbow Connection Diagram

The bandwidth problem is also solved through use of the Crossbow ASIC. The Crossbow acts a switch which connects every device in the system to every other device. Each device has a port which can communicate only with the Crossbow. The Crossbow in turn allows all of the devices to communicate with one another.

The Crossbow ASIC contains eight device ports. Seven ports are implemented on the OCTANE system as shown in Figure 2.2. Each port contains a dedicated 16-bit input and 16-bit output. With a 400MHz data rate, each port can operate at a peak bandwidth of 800MB per second in and 800MB per second out. Because these ports transfer information independent of one another, this allows for a maximum peak bandwidth of 1.6GB per second, which easily supports multiple streams of digital video.

# 2.1.2 OCTANE Board Layout

In order for the OCTANE system to support such high frequencies, parameters such as edge rates, transmission lines, characteristic impedance, signal reflections, and crosstalk, accorded little or no attention in lower-frequency systems, had to be tightly controlled during layout. In order for the OCTANE system to operate properly at these high frequencies, the following design issues had to be addressed:

- preservation of signal integrity by tight control of transmission line effects

- minimization of clock skew in the system

- mitigation of potential ground-bounce problems

At such high frequencies, every signal trace on the OCTANE system board has the ability to become a transmission line. An ideal transmission line is one where there is never any loss or distortion of the signal. Resistance in the signal trace is non-existent. The principle properties of a transmission line are its characteristic impedance and propagation delay per unit of

#### **OCTANE** System Architecture

measure. Unfortunately, this ideal scenario does not exist. The fact is, transmission lines generate undesirable effects such as those listed above, creating an overall loss in both signal integrity and performance.

# 2.1.3 Packet Switching

The OCTANE system implements a packet-switched data transfer protocol for transferring data between the various devices in the system. This differs from the traditional "circuit-switched" protocol implemented in shared-bus architectures. In a circuit-switched protocol, once a connection between the two devices in the system has been established, no other ports on the system can talk to these devices. For example, once one of the peripheral devices has gained control of the bus to communicate with the CPU, none of the other peripherals in the system may use the bus to communicate with either the CPU or one another until the current transaction has completed.

In a packet-switched protocol, packets are defined as short bursts of information which are transferred between devices via a split-transaction protocol. The split-transaction protocol allows for multiple outstanding transactions on a given Crossbow link. The fundamental packet size is 128 bytes. Refer to Section 2.1.4 and Section 2.3.1.1 for more information on the packet-switched protocol.

# 2.1.4 Unfair Arbitration

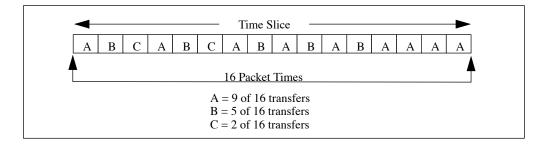

A time slice is made up of a number of packet times. Figure 2.3 shows an example of a time slice containing 16 packets. Each letter represents a port on the Crossbow.

In Figure 2.3, the time slice is shown as 16 packet-times long. In this example, nine packets have been allocated to Device A, five packets to Device B, and two packets to Device C. Once a device has used its allocation, it must wait for the next time slice to send more data. For example, Device C was allotted two packets. Once the second packet is sent, Device C must wait for a new time slice before sending any subsequent packets.

Figure 2.3 Packet-Switched Protocol

Devices A and B still have time left. Once Device B finishes its allocation, the remainder of the packets for this time slice can only be used by Device A. This is called "guaranteed unfair arbi-

tration" and allows streams to be prioritized. In the OCTANE system the most important streams from certain devices can be given priority over other devices. With one arbiter per port, the device priority in the OCTANE system is fully programmable.

#### 2.1.5 Guaranteed Bandwidth and Latency

The Crossbow ASIC guarantees a worst-case average latency through support of a dual priority arbitration scheme. These dual arbiters are defined as the Guaranteed Bandwidth Ring (GBR) and the Remainder Ring (RR). A packet on the GBR, or high-priority bandwidth ring, will be transferred before a packet on the RR, or normal-priority ring. Each device is allowed to transfer a certain amount of packets per a given amount of time, as shown in Figure 2.3 above. The GBR ring is allowed to transfer one packet per time slice, whereas the RR ring is programmable from one to eight packets per time slice. This scheme defines a maximum number of packets which can be sent before a packet on the GBR is guaranteed to be transferred. This is called "Guaranteed Latency".

Devices on the GBR are allocated a given number of packets per time slice. The number of packets allowed by a given device per time interval is determined by the bandwidth counter which is set based on the types and priority of the transfers. A packet is eligible to participate in GBR arbitration if the corresponding GBR enable bit is set and the associated bandwidth counter (BWC) value is greater than zero. The BWC is decremented each time a request packet is transferred. When the BWC decrements to zero, that device falls from the GBR to the RR.

In Figure 2.3 for example, Device A is allocated 9 of 16 packets for the given time slice. However, there is no guarantee that Device A will use all 9 allocated packets. If this should occur, the remaining packets go to the RR. Therefore, if Devices B or C wish to send additional packets and they are available in the remainder ring, these two devices go through arbitration to determine which devices get which number of the remaining packets. The remainder ring is mostly used by devices which have not been allocated to the GBR.

Arbitration within the RR is done using a weighted arbitration scheme. Each device on the RR is allocated a number between one and eight. This value corresponds to the number of consecutive transfers allowed by that device before the RR arbiter grants the next requesting device.

The two-ring arbitration approach allows devices to be guaranteed a percentage of the available bandwidth taken from the GBR, and a distributed portion of the RR if more requests exist. Those devices that can tolerate latency in the transfer rate are not considered high-priority transfers, hence the corresponding bandwidth counter is set to zero and the device may only participate in the RR arbitration.

# 2.1.6 Data Transfer Types

Fundamental sizes for read requests are cache lines (128 bytes), quarter-cache lines (32 bytes), and doublewords (8 bytes).

A write request contains information regarding the target device, the fact that the cycle is a write, and how much data is being transferred. In the case of a write the response can be op-

tional. A 'Fire and Forget' write sends data and does not wait for a response from the target device verifying that the data has arrived.

If ordering is important, as is the case when multiple devices work on the same task and deliver the results to another device, a 'Write-with-Response' transfer protocol can be used. For example, Device A writes to Device B, and Device B returns a response. Device A then informs Device C that this transfer has completed successfully.

# 2.1.7 Link Level Protocol

The OCTANE system implements a 'Link Level Protocol' (LLP). This protocol consists of dedicated hardware which guarantees error-free delivery. In the LLP, the sending device breaks the data to be sent into 128-bit micropackets. Each micro-packet is tagged with a Cyclical Redundancy Check (CRC) value and a sequence number. The receiver checks the CRC value and acknowledges reception of the packet. If there is an error, the receiver logs the sequence number and asks the sender to retry that micro-packet. This is where the two links between the devices work well. Each CRC per micropacket is checked by the receiver. If a packet has an error, all subsequent packets in transit after the one that caused the error are ignored. The sender then re-sends the packet that caused the error. This packet is retried a programmed number of times. If data does not send correctly after the timer times out, an interrupt is generated.

This system is superior to both Error Checking and Correction (ECC) and parity. With ECC the error can be detected, but only single-bit errors can be corrected. With parity, a single-bit error can be detected but not corrected. The LLP protocol works even under severe conditions, such as when the links are operating at different speeds.

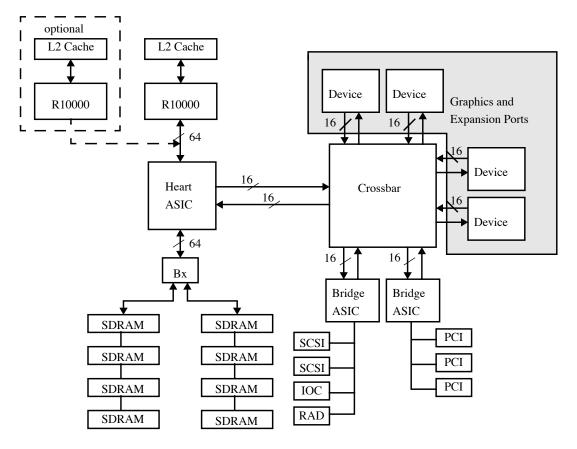

# 2.1.8 System Modularity

The OCTANE system decouples the processor and memory from the rest of the I/O subsystem. The processor interfaces to the Crossbow ASIC through the Heart ASIC, which connects to one of the Crossbow ports as shown in Figure 2.4. Note that there is no direct connection between the processor/memory system, and the I/O subsystem. Therefore, next generation processor or memory devices can be easily adapted without requiring changes to the I/O system. In addition, the OCTANE system supports both single- and dual-processor configurations. Figure 2.4 shows a block diagram of the OCTANE system.

Figure 2.4 OCTANE System Block Diagram